Электроника:Цифровая электроника/Мультивибраторы/D-защёлка: различия между версиями

Valemak (обсуждение | вклад) (Новая страница: «{{Панель управления/Электроника}} {{Перевод от valemak}} {{Myagkij-редактор}} =D-защёлка<ref>[https://www.alla...») |

Нет описания правки |

||

| Строка 37: | Строка 37: | ||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 43: | Строка 43: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника | {{Навигационная таблица/Портал/Электроника}} | ||

Текущая версия от 21:52, 22 мая 2023

D-защёлка[1]

Поскольку вход разрешения на вентильной SR-защёлке позволяет зафиксировать выходы Q и НЕ-Q независимо от состояний S или R, мы можем исключить один из этих входов, чтобы создать схему триггера мультивибратора, исключив таким образом саму возможность «недопустимого» входного состояния.

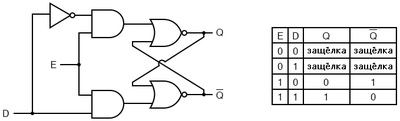

Такая схема называется D-защёлкой, и её логика выглядит следующим образом:

Обратите внимание, что вход R был заменён дополнением (инверсией) старого входа S, а вход S переименован в D. Как и в случае вентильной SR-защёлки, D-защёлка не реагирует на входной сигнал, если разрешающий вход равен 0 – он просто остаётся зафиксированным в своем последнем состоянии. Однако, когда вход разрешения равен 1, выход Q соответствует входу D.

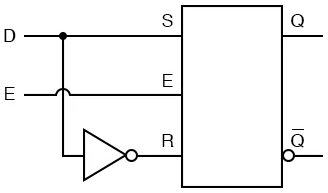

Поскольку вход R в SR-схеме устранён, в этой защёлке не может возникнуть «недействительное» или «недопустимое» состояния. Q и НЕ-Q всегда будут противоположны друг другу. Если приведённая выше диаграмма сбивает с толку, следующая диаграмма должна внести ясность:

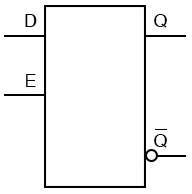

Подобно SR-защёлкам (в том числе и вентильным), на схемах D-защёлки стандартно обозначаются в виде отдельного блока:

D-защёлка – это не что иное, как вентильная SR-защёлка с добавленным инвертором, делающим вход R дополнением (инверсией) S.

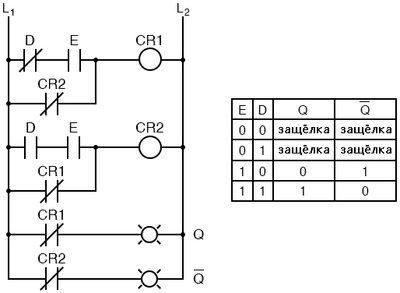

Давайте рассмотрим релейный эквивалент D-защёлки, модифицированный на основе базовой лестничной схемы SR-защёлки:

Примером применения для D-защёлки является 1-битная схема памяти. Можно «записать» (сохранить) бит 0 или 1 в этой схеме защёлки, установив на входе разрешения высокий уровень (1) и установив D на требуемое значение (равное состоянию хранимого бита). Когда на разрешающем входе установлен низкий уровень (0), защёлка игнорирует состояние входа D и удерживает сохранённое значение бита, выдавая его в Q и обратное значение на выход НЕ-Q.

Итог

- D-защёлка схожа с SR-защёлкой, имеющей только один вход (обычно обозначаемый «D»). Активация входа D приводит схему в состояние «Установка», а деактивация – в состояние «Сброс». Конечно, это только в том случае, если вход разрешения (E) также активирован. В противном случае выход(-ы) будет заблокирован, не реагируя на состояние входа D.

- D-защёлки могут использоваться как 1-битные схемы памяти, сохраняя либо «высокое», либо «низкое» состояние, которое было в момент отключения, и «считывая» новые данные с входа D при включении.

См.также

Внешние ссылки