Электроника:Цифровая электроника/Логические вентили/«Буферные» вентили: различия между версиями

Valemak (обсуждение | вклад) (Новая страница: «{{Панель управления/Электроника}} {{Перевод от valemak}} {{Myagkij-редактор}} =«Буферные» вентили<re...») |

Нет описания правки |

||

| (не показано 5 промежуточных версий 2 участников) | |||

| Строка 9: | Строка 9: | ||

[[File:IV-3_3_1.png|400px|center|thumb|'''Рис. 1.''' Двойная инверсия, эквивалентная отсутствию инверсии.|alt=Рис. 1. Двойная инверсия, эквивалентная отсутствию инверсии.]] | [[File:IV-3_3_1.png|400px|center|thumb|'''Рис. 1.''' Двойная инверсия, эквивалентная отсутствию инверсии.|alt=Рис. 1. Двойная инверсия, эквивалентная отсутствию инверсии.]] | ||

Хотя | Хотя эта взаимная аннигиляция инверсий может показаться бессмысленной, этому есть практическое применение. Ведь, как вы помните, вентильные схемы всегда являются усилителями сигнала, независимо от того, какую логическую функцию они реализуют. | ||

Источник слишком слабого сигнала (то есть такого, который не может слишком большой ток передавать нагрузке или потреблять от неё) может быть усилен с помощью двух | Источник слишком слабого сигнала (то есть такого, который не может слишком большой ток передавать нагрузке или потреблять от неё) может быть усилен с помощью двух [[инвертор]]ов, вроде той пары, что показана на предыдущем рисунке. Логический уровень не изменился, но при этом все возможности последнего инвертора по подаче или потреблению тока доступны для управления сопротивлением нагрузки, если это необходимо. | ||

Для этой цели служит специальный логический вентиль, называемый ''буфером'', выполняющий ту же функцию, что и два последовательных инвертора. Его схемное обозначение – это просто треугольник без «пузырька» на выводе выхода: | Для этой цели служит специальный логический вентиль, называемый ''буфером'', выполняющий ту же функцию, что и два последовательных инвертора. Его схемное обозначение – это просто треугольник без «пузырька» на выводе выхода: | ||

| Строка 19: | Строка 19: | ||

== Буферная схема с выходом с открытым коллектором == | == Буферная схема с выходом с открытым коллектором == | ||

Внутри более глобальной цепи принципиальная схема типичного буфера с открытым | Внутри более глобальной цепи принципиальная схема типичного буфера с открытым [[коллектор]]ом не сильно отличается от схемы простого [[инвертор]]а: добавляется только ещё один транзисторный каскад с общим эмиттером для обратного инвертирования выходного сигнала. | ||

[[File:IV-3_3_3.jpg|400px|center|thumb|'''Рис. 3.''' Буферная схема с выходом с открытым коллектором.|alt=Рис. 3. Буферная схема с выходом с открытым коллектором.]] | [[File:IV-3_3_3.jpg|400px|center|thumb|'''Рис. 3.''' Буферная схема с выходом с открытым коллектором.|alt=Рис. 3. Буферная схема с выходом с открытым коллектором.]] | ||

| Строка 29: | Строка 29: | ||

[[File:IV-3_3_4.png|400px|center|thumb|'''Рис. 4.''' Анализ «высокого» входа: входной логический уровень равен «1».|alt=Рис. 4. Анализ «высокого» входа: входной логический уровень равен «1».]] | [[File:IV-3_3_4.png|400px|center|thumb|'''Рис. 4.''' Анализ «высокого» входа: входной логический уровень равен «1».|alt=Рис. 4. Анализ «высокого» входа: входной логический уровень равен «1».]] | ||

Как и в схеме | Как и в схеме [[инвертор]]а, что мы рассмотрели раннее, «высокий» вход не вызывает проводимости через левый управляющий диод Q<sub>1</sub> (P-N-переход эмиттер/база). Весь ток R<sub>1</sub> проходит через базу транзистора Q<sub>2</sub>, насыщая его: | ||

[[File:IV-3_3_5.png|400px|center|thumb|'''Рис. 5.''' «Высокий» вход не вызывает проводимости через левый управляющий диод Q<sub>1</sub> (P-N-переход эмиттер/база).|alt=Рис. 5. «Высокий» вход не вызывает проводимости через левый управляющий диод Q1 (P-N-переход эмиттер/база).]] | [[File:IV-3_3_5.png|400px|center|thumb|'''Рис. 5.''' «Высокий» вход не вызывает проводимости через левый управляющий [[диод]] Q<sub>1</sub> (P-N-переход эмиттер/база).|alt=Рис. 5. «Высокий» вход не вызывает проводимости через левый управляющий диод Q1 (P-N-переход эмиттер/база).]] | ||

Насыщение Q<sub>2</sub> приводит к насыщению и Q<sub>3</sub>, что приводит к очень небольшому падению напряжения между базой и | Насыщение Q<sub>2</sub> приводит к насыщению и Q<sub>3</sub>, что приводит к очень небольшому падению напряжения между базой и [[эмиттер]]ом оконечного выходного [[транзистор]]а Q<sub>4</sub>. Таким образом, Q<sub>4</sub> будет находиться в режиме отсечки, не проводя тока. | ||

Выходной вывод будет «плавающим» (не соединённым ни с «землёй», ни с V<sub> | Выходной вывод будет «плавающим» (не соединённым ни с «землёй», ни с V<sub>КК</sub>), и это будет эквивалентно «высокому» состоянию на входе следующего ТТЛ-элемента, на который он подаётся. Таким образом, «высокий» вход даёт также «высокий» выход. | ||

== Анализ «низкого» входа == | == Анализ «низкого» входа == | ||

| Строка 43: | Строка 43: | ||

[[File:IV-3_3_6.png|400px|center|thumb|'''Рис. 6.''' «Низкий» входной сигнал (входной вывод заземлён).|alt=Рис. 6. «Низкий» входной сигнал (входной вывод заземлён).]] | [[File:IV-3_3_6.png|400px|center|thumb|'''Рис. 6.''' «Низкий» входной сигнал (входной вывод заземлён).|alt=Рис. 6. «Низкий» входной сигнал (входной вывод заземлён).]] | ||

Теперь весь ток R<sub>1</sub> отводится через входной переключатель, что устраняет базовый ток в Q<sub>2</sub>. Это приводит к отключению | Теперь весь ток R<sub>1</sub> отводится через входной переключатель, что устраняет базовый ток в Q<sub>2</sub>. Это приводит к отключению [[транзистор]]а Q<sub>2</sub>, в результате чего ток базы также не проходит и через Q<sub>3</sub>. | ||

С учётом отсечки Q<sub>3</sub> также Q<sub>4</sub> будет насыщаться током через резистор R<sub>4</sub>, таким образом соединяя выход с «землёй», устанавливая на нём «низкий» логический уровень. Таким образом, «низкий» вход даёт также «низкий» выход. | С учётом отсечки Q<sub>3</sub> также Q<sub>4</sub> будет насыщаться током через резистор R<sub>4</sub>, таким образом соединяя выход с «землёй», устанавливая на нём «низкий» логический уровень. Таким образом, «низкий» вход даёт также «низкий» выход. | ||

| Строка 49: | Строка 49: | ||

== Принципиальная схема с транзисторным выходом «тотемный столб» == | == Принципиальная схема с транзисторным выходом «тотемный столб» == | ||

Принципиальная схема буфера с выходными | Принципиальная схема буфера с выходными [[транзистор]]ами типа «тотемный столб» несколько сложнее, но основные принципы и, конечно же, таблица истинности те же, что и для схемы с выходом с открытым [[коллектор]]ом: | ||

[[File:IV-3_3_7.png|400px|center|thumb|'''Рис. 7.''' Принципиальная схема выходных | [[File:IV-3_3_7.png|400px|center|thumb|'''Рис. 7.''' Принципиальная схема выходных [[транзистор]]ов «тотемный столб».|alt=Рис. 7. Принципиальная схема выходных транзисторов «тотемный столб».]] | ||

== Итог == | == Итог == | ||

*Два инвертора (пара вентилей НЕ), соединенные «последовательно», чтобы сначала инвертировать, а затем ре-инвертировать двоичный бит, выполняют функцию ''буфера''. ''Буферные вентили'' служат для усиления сигнала: берётся «слабый» источник сигнала, не способный обеспечить или потреблять большой ток, и повышается до сигнала такого уровня, чтобы была возможность управлять нагрузкой. | * Два инвертора (пара вентилей НЕ), соединенные «последовательно», чтобы сначала инвертировать, а затем ре-инвертировать двоичный бит, выполняют функцию ''буфера''. ''Буферные вентили'' служат для усиления сигнала: берётся «слабый» источник сигнала, не способный обеспечить или потреблять большой ток, и повышается до сигнала такого уровня, чтобы была возможность управлять нагрузкой. | ||

*Буферные вентили в схемах изображаются в виде треугольника без «пузырька», обозначающего инвертор. | * [[Буферные вентили]] в схемах изображаются в виде треугольника без «пузырька», обозначающего [[инвертор]]. | ||

*Буферы, как и простые | * Буферы, как и простые [[инвертор]]ы, могут быть реализованы с выходом с открытым коллектором или с выходом типа «тотемный столб». | ||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 67: | Строка 67: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника}} | {{Навигационная таблица/Портал/Электроника}} | ||

[[Категория:Цифровая электроника]] | [[Категория:Цифровая электроника]] | ||

[[Категория:Логические вентили]] | [[Категория:Логические вентили]] | ||

[[Категория:Вентили «НЕ»]] | [[Категория:Вентили «НЕ»]] | ||

[[Категория:«Буферные» вентили]] | |||

Текущая версия от 21:51, 22 мая 2023

«Буферные» вентили[1]

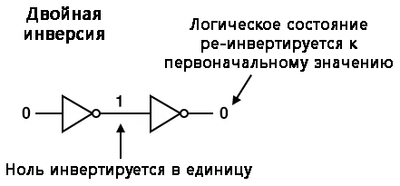

Если бы мы соединили два инверторных вентиля вместе таким образом, чтобы выход одного подавался на вход другого, две функции инверсии «нейтрализовали» бы друг друга, в результате чего не будет общей инверсии от изначального входа к конечному выходу:

Хотя эта взаимная аннигиляция инверсий может показаться бессмысленной, этому есть практическое применение. Ведь, как вы помните, вентильные схемы всегда являются усилителями сигнала, независимо от того, какую логическую функцию они реализуют.

Источник слишком слабого сигнала (то есть такого, который не может слишком большой ток передавать нагрузке или потреблять от неё) может быть усилен с помощью двух инверторов, вроде той пары, что показана на предыдущем рисунке. Логический уровень не изменился, но при этом все возможности последнего инвертора по подаче или потреблению тока доступны для управления сопротивлением нагрузки, если это необходимо.

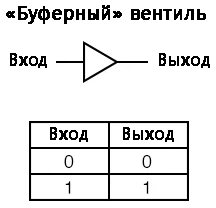

Для этой цели служит специальный логический вентиль, называемый буфером, выполняющий ту же функцию, что и два последовательных инвертора. Его схемное обозначение – это просто треугольник без «пузырька» на выводе выхода:

Буферная схема с выходом с открытым коллектором

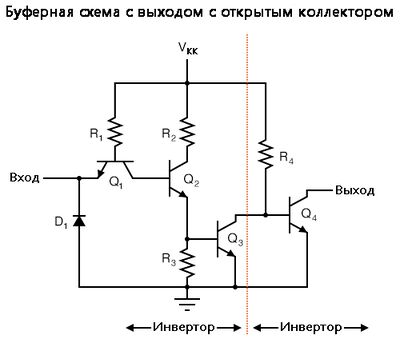

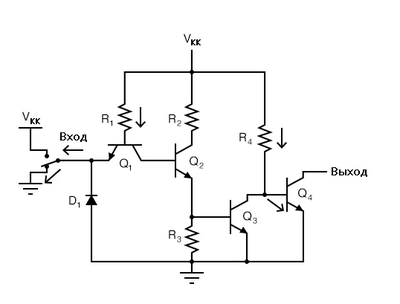

Внутри более глобальной цепи принципиальная схема типичного буфера с открытым коллектором не сильно отличается от схемы простого инвертора: добавляется только ещё один транзисторный каскад с общим эмиттером для обратного инвертирования выходного сигнала.

Анализ «высокого» входа

Давайте проанализируем эту схему для двух условий: если входной логический уровень равен «1», и если входной логический уровень равен «0». Во-первых, посмотрим «высокий» (= 1) вход:

Как и в схеме инвертора, что мы рассмотрели раннее, «высокий» вход не вызывает проводимости через левый управляющий диод Q1 (P-N-переход эмиттер/база). Весь ток R1 проходит через базу транзистора Q2, насыщая его:

Насыщение Q2 приводит к насыщению и Q3, что приводит к очень небольшому падению напряжения между базой и эмиттером оконечного выходного транзистора Q4. Таким образом, Q4 будет находиться в режиме отсечки, не проводя тока.

Выходной вывод будет «плавающим» (не соединённым ни с «землёй», ни с VКК), и это будет эквивалентно «высокому» состоянию на входе следующего ТТЛ-элемента, на который он подаётся. Таким образом, «высокий» вход даёт также «высокий» выход.

Анализ «низкого» входа

При «низком» входном сигнале (т.е. входной вывод заземлён) анализ выглядит примерно так:

Теперь весь ток R1 отводится через входной переключатель, что устраняет базовый ток в Q2. Это приводит к отключению транзистора Q2, в результате чего ток базы также не проходит и через Q3.

С учётом отсечки Q3 также Q4 будет насыщаться током через резистор R4, таким образом соединяя выход с «землёй», устанавливая на нём «низкий» логический уровень. Таким образом, «низкий» вход даёт также «низкий» выход.

Принципиальная схема с транзисторным выходом «тотемный столб»

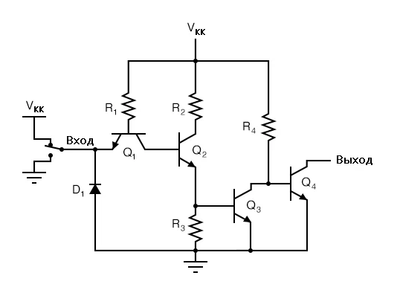

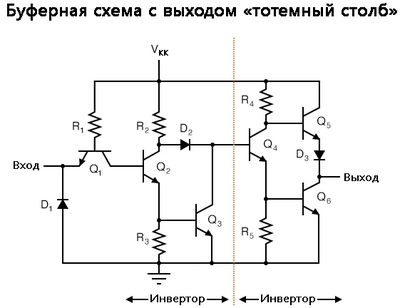

Принципиальная схема буфера с выходными транзисторами типа «тотемный столб» несколько сложнее, но основные принципы и, конечно же, таблица истинности те же, что и для схемы с выходом с открытым коллектором:

Итог

- Два инвертора (пара вентилей НЕ), соединенные «последовательно», чтобы сначала инвертировать, а затем ре-инвертировать двоичный бит, выполняют функцию буфера. Буферные вентили служат для усиления сигнала: берётся «слабый» источник сигнала, не способный обеспечить или потреблять большой ток, и повышается до сигнала такого уровня, чтобы была возможность управлять нагрузкой.

- Буферные вентили в схемах изображаются в виде треугольника без «пузырька», обозначающего инвертор.

- Буферы, как и простые инверторы, могут быть реализованы с выходом с открытым коллектором или с выходом типа «тотемный столб».

См.также

Внешние ссылки