Электроника:Цифровая электроника/Логические вентили/Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»: различия между версиями

Myagkij (обсуждение | вклад) Нет описания правки |

Нет описания правки |

||

| (не показаны 4 промежуточные версии 2 участников) | |||

| Строка 5: | Строка 5: | ||

=Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-3/ttl-nand-and-gates/ www.allaboutcircuits.com - TTL NAND and AND gates]</ref>= | =Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-3/ttl-nand-and-gates/ www.allaboutcircuits.com - TTL NAND and AND gates]</ref>= | ||

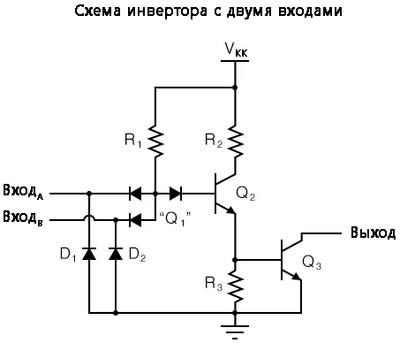

Изменим нашу базовую схему | Изменим нашу базовую схему [[инвертор]]а с выходом с открытым коллектором, добавив ещё один входной вывод точно такой же, как и первый: | ||

[[File:IV-3_5_1.png|400px|center|thumb|'''Рис. 1.''' Видоизменённая схема (добавлен ещё один вход) | [[File:IV-3_5_1.png|400px|center|thumb|'''Рис. 1.''' Видоизменённая схема (добавлен ещё один вход) [[инвертор]]а с выходом с открытым [[коллектор]]ом.|alt=Рис. 1. Видоизменённая схема (добавлен ещё один вход) инвертора с выходом с открытым коллектором.]] | ||

Подобная схема часто используются на практике, и было бы логично, её называть «''двухвходным инвертором''». Сейчас мы проанализируем эту схему, определим, какую именно логическую функцию она выполняет и, соответственно, как её следует обозначать. | Подобная схема часто используются на практике, и было бы логично, её называть «''двухвходным инвертором''». Сейчас мы проанализируем эту схему, определим, какую именно логическую функцию она выполняет и, соответственно, как её следует обозначать. | ||

Так же, как в случае | Так же, как в случае [[инвертор]]а и буфера, [[кластер]] «управляющих» [[диод]]ов, помеченный как «Q<sub>1</sub>», фактически формирует [[транзистор]], даже если он не используется в качестве усилителя. К сожалению, простая [[NPN-структура]] [[транзистор]]а недостаточна для моделирования трёх [[P-N-переход]]ов, необходимых в этой диодной сети, поэтому требуется другой [[транзистор]] (и другой символ для него). | ||

Такой транзистор имеет один коллектор, одну базу и два | Такой [[транзистор]] имеет один [[коллектор]], одну базу и два [[эмиттер]]а, а в схеме он выглядит так: | ||

[[File:IV-3_5_2.png|400px|center|thumb|'''Рис. 2.''' На схеме кластер | [[File:IV-3_5_2.png|400px|center|thumb|'''Рис. 2.''' На схеме кластер [[диод]]ов Q<sub>1</sub> переобозначили как единый [[транзистор]] (с двумя [[эмиттер]]ами).|alt=Рис. 2. На схеме кластер диодов Q1 переобозначили как единый транзистор (с двумя эмиттерами).]] | ||

Если в схеме всего один вход (как в | Если в схеме всего один вход (как в [[инвертор]]е), то его заземление приводит к «высокому» выходу (1). В случае конфигурации с выходом с открытым [[коллектор]]ом это «высокое» состояние было бы просто «плавающим». | ||

Разрешение входу «плавать» (или другими словами, быть подключённым к V<sub> | Разрешение входу «плавать» (или другими словами, быть подключённым к V<sub>КК</sub>) привело бы к тому, что выход стал заземлённым, что соответствует «низкому» (нулевому) состоянию. Таким образом, вход 1 даёт выход 0, и наоборот. | ||

Поскольку эта схема очень похожа на простую схему | Поскольку эта схема очень похожа на простую схему [[инвертор]]а, с той лишь разницей, что второй входной вывод подключён таким же образом к базе [[транзистор]]а Q<sub>2</sub>, то можно утверждать, что каждый из входов имеет одинаковое влияние на выход. | ||

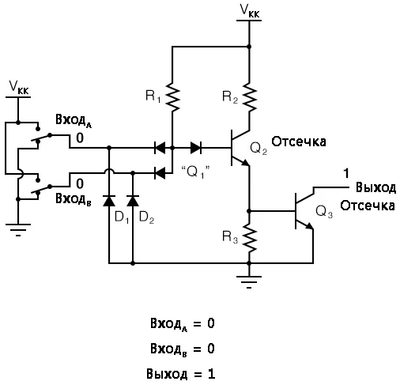

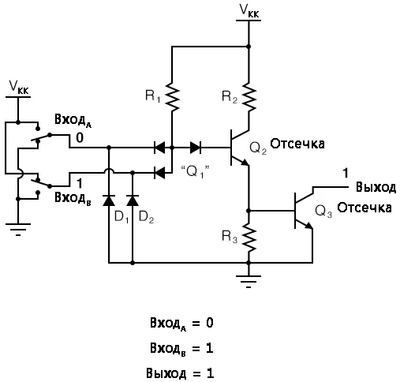

А именно, если какой-либо из входов заземлён, транзистор Q<sub>2</sub> будет принудительно переведён в состояние отсечки, таким образом выключив Q<sub>3</sub> и высвобождая выход (выход становится «высоким»). Следующая серия иллюстраций показывает это для трёх возможных входных состояний (00, 01 и 10): | А именно, если какой-либо из входов заземлён, [[транзистор]] Q<sub>2</sub> будет принудительно переведён в состояние отсечки, таким образом выключив Q<sub>3</sub> и высвобождая выход (выход становится «высоким»). Следующая серия иллюстраций показывает это для трёх возможных входных состояний (00, 01 и 10): | ||

{| class="wikitable" style="margin:0 auto" | {| class="wikitable" style="margin:0 auto" | ||

|- | |- | ||

| [[File:IV-3_5_3.png| | | [[File:IV-3_5_3.png|400px|center|thumb|'''Рис. 3.''' «Высокий» выход, т.к. оба входа «низкие». |alt=Рис. 3. «Высокий» выход, т.к. оба входа «низкие».]] || [[File:IV-3_5_4.png|400px|center|thumb|'''Рис. 4.''' «Высокий» выход, т.к. один из входов «низкий».|alt=Рис. 4. «Высокий» выход, т.к. один из входов «низкий».]] || [[File:IV-3_5_5.png|400px|center|thumb|'''Рис. 5.''' «Высокий» выход, т.к. один из входов «низкий».|alt=Рис. 5. «Высокий» выход, т.к. один из входов «низкий».]] | ||

|} | |} | ||

В любом случае, когда есть заземлённый («низкий») вход, выход гарантированно будет «плавающим» (а значит, «высоким»). И наоборот, только в том случае выход будет «низкий», если транзистор Q<sub>3</sub> включится, а это возможно, когда транзистор Q<sub>2</sub> будет включён (насыщен), что означает, что ни один из входов не может отводить ток R<sub>1</sub> от базы Q<sub>2</sub>. | В любом случае, когда есть заземлённый («низкий») вход, выход гарантированно будет «плавающим» (а значит, «высоким»). И наоборот, только в том случае выход будет «низкий», если [[транзистор]] Q<sub>3</sub> включится, а это возможно, когда [[транзистор]] Q<sub>2</sub> будет включён (насыщен), что означает, что ни один из входов не может отводить ток R<sub>1</sub> от базы Q<sub>2</sub>. | ||

Единственное условие, удовлетворяющее этому требованию – когда оба входа «высокие» (1): | Единственное условие, удовлетворяющее этому требованию – когда оба входа «высокие» (1): | ||

| Строка 38: | Строка 38: | ||

== Вентиль «И-НЕ» == | == Вентиль «И-НЕ» == | ||

Собрав и сведя эти результаты воедино в таблицу истинности, видим, что этот шаблон соответствует логическому элементу И-НЕ: | Собрав и сведя эти результаты воедино в таблицу истинности, видим, что этот шаблон соответствует логическому [[элементу И-НЕ]]: | ||

[[File:IV-3_5_7.png|400px|center|thumb|'''Рис. 7.''' Вентили И-НЕ – это тип вентиля, когда к выходу логического элемента И добавлен инвертор.|alt=Рис. 7. Вентили И-НЕ – это тип вентиля, когда к выходу логического элемента И добавлен инвертор.]] | [[File:IV-3_5_7.png|400px|center|thumb|'''Рис. 7.''' [[Вентили И-НЕ]] – это тип вентиля, когда к выходу логического элемента И добавлен [[инвертор]].|alt=Рис. 7. Вентили И-НЕ – это тип вентиля, когда к выходу логического элемента И добавлен инвертор.]] | ||

В предыдущем разделе, там где мы разбираем «И-НЕ», этот тип вентиля был создан, когда мы взяли логический элемент И и усложнили его, добавив к выходу инвертор (элемент НЕ). Однако, если вникнуть в схему на рисунках 2-6, то увидим, что данная ТТЛ-конструкция – самый простой и естественный аппаратный способ реализовать функцию И-НЕ. | В предыдущем разделе, там где мы разбираем «И-НЕ», этот тип вентиля был создан, когда мы взяли логический элемент И и усложнили его, добавив к выходу инвертор (элемент НЕ). Однако, если вникнуть в схему на рисунках 2-6, то увидим, что данная ТТЛ-конструкция – самый простой и естественный аппаратный способ реализовать функцию И-НЕ. | ||

Чтобы реализовать функцию И с использованием ТТЛ-схемы, нужно немного усложнить эту схему, каскадно добавив к выходу инвертор, точно так же, как мы добавляли дополнительный транзисторный каскад в ТТЛ-схему инвертора, когда превращали его в «буфер»: | Чтобы реализовать функцию И с использованием ТТЛ-схемы, нужно немного усложнить эту схему, каскадно добавив к выходу инвертор, точно так же, как мы добавляли дополнительный транзисторный каскад в ТТЛ-схему инвертора, когда превращали его в «буфер»: | ||

[[File:IV-3_5_8.png|400px|center|thumb|'''Рис. 8.''' Вентиль И с выходом с открытым | [[File:IV-3_5_8.png|400px|center|thumb|'''Рис. 8.''' Вентиль И с выходом с открытым [[коллектор]]ом.|alt=Рис. 8. Вентиль И с выходом с открытым коллектором.]] | ||

== Вентиль «И» == | == Вентиль «И» == | ||

| Строка 51: | Строка 52: | ||

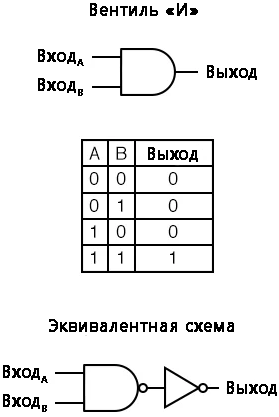

Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом) показаны здесь: | Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом) показаны здесь: | ||

[[File:IV-3_5_9.png|400px|center|thumb|'''Рис. 9.''' Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом).|alt=Рис. 9. Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом).]] | [[File:IV-3_5_9.png|400px|center|thumb|'''Рис. 9.''' Таблица истинности и эквивалентная схема ([[вентиль И-НЕ с инвертированным выходом]]).|alt=Рис. 9. Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом).]] | ||

Само собой, схемы вентилей И-НЕ и ИЛИ можно спроектировать с каскадным выходом типа «тотемный столб», а не с выходом с открытым | Само собой, схемы [[вентилей И-НЕ]] и ИЛИ можно спроектировать с каскадным выходом типа «тотемный столб», а не с выходом с открытым [[коллектор]]ом. Версии с выходом с открытым [[коллектор]]ом несколько проще, поэтому их я и предпочитаю использовать в качестве примеров. | ||

== Итог == | == Итог == | ||

*Вентиль И-НЕ можно создать, взяв ТТЛ-схему | * [[Вентиль И-НЕ]] можно создать, взяв [[ТТЛ]]-схему [[инвертор]]а и добавив ещё один вход. | ||

*Вентиль И можно создать, каскадно добавив инвертор к выходу в ТТЛ-схему вентиля И-НЕ. | * [[Вентиль И]] можно создать, каскадно добавив инвертор к выходу в [[ТТЛ]]-схему [[вентиля И-НЕ]]. | ||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 68: | Строка 69: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника}} | {{Навигационная таблица/Портал/Электроника}} | ||

[[Категория:Цифровая электроника]] | [[Категория:Цифровая электроника]] | ||

[[Категория: | [[Категория:Логические вентили]] | ||

[[Категория: | [[Категория:Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»]] | ||

[[Категория: | [[Категория:Вентиль «И»]] | ||

[[Категория: | [[Категория:Вентиль «И-НЕ»]] | ||

Текущая версия от 21:52, 22 мая 2023

Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»[1]

Изменим нашу базовую схему инвертора с выходом с открытым коллектором, добавив ещё один входной вывод точно такой же, как и первый:

Подобная схема часто используются на практике, и было бы логично, её называть «двухвходным инвертором». Сейчас мы проанализируем эту схему, определим, какую именно логическую функцию она выполняет и, соответственно, как её следует обозначать.

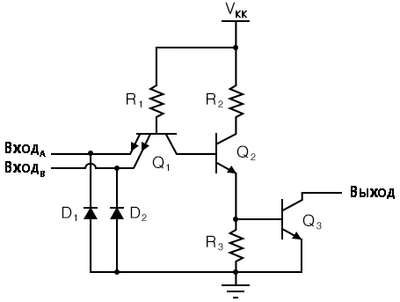

Так же, как в случае инвертора и буфера, кластер «управляющих» диодов, помеченный как «Q1», фактически формирует транзистор, даже если он не используется в качестве усилителя. К сожалению, простая NPN-структура транзистора недостаточна для моделирования трёх P-N-переходов, необходимых в этой диодной сети, поэтому требуется другой транзистор (и другой символ для него).

Такой транзистор имеет один коллектор, одну базу и два эмиттера, а в схеме он выглядит так:

Если в схеме всего один вход (как в инверторе), то его заземление приводит к «высокому» выходу (1). В случае конфигурации с выходом с открытым коллектором это «высокое» состояние было бы просто «плавающим».

Разрешение входу «плавать» (или другими словами, быть подключённым к VКК) привело бы к тому, что выход стал заземлённым, что соответствует «низкому» (нулевому) состоянию. Таким образом, вход 1 даёт выход 0, и наоборот.

Поскольку эта схема очень похожа на простую схему инвертора, с той лишь разницей, что второй входной вывод подключён таким же образом к базе транзистора Q2, то можно утверждать, что каждый из входов имеет одинаковое влияние на выход.

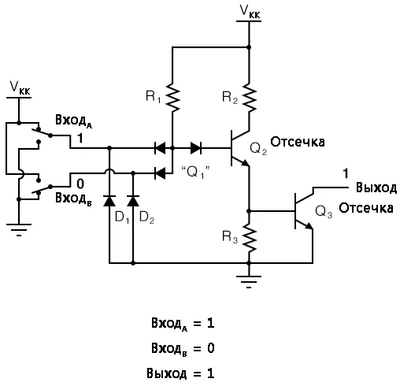

А именно, если какой-либо из входов заземлён, транзистор Q2 будет принудительно переведён в состояние отсечки, таким образом выключив Q3 и высвобождая выход (выход становится «высоким»). Следующая серия иллюстраций показывает это для трёх возможных входных состояний (00, 01 и 10):

|

|

|

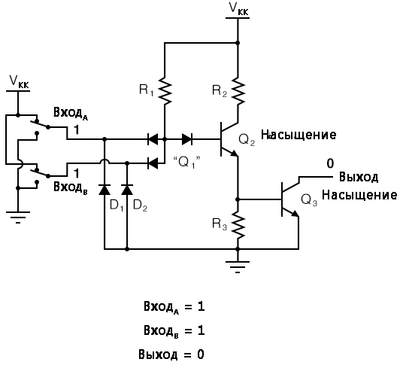

В любом случае, когда есть заземлённый («низкий») вход, выход гарантированно будет «плавающим» (а значит, «высоким»). И наоборот, только в том случае выход будет «низкий», если транзистор Q3 включится, а это возможно, когда транзистор Q2 будет включён (насыщен), что означает, что ни один из входов не может отводить ток R1 от базы Q2.

Единственное условие, удовлетворяющее этому требованию – когда оба входа «высокие» (1):

Вентиль «И-НЕ»

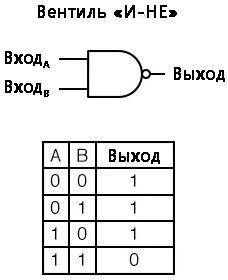

Собрав и сведя эти результаты воедино в таблицу истинности, видим, что этот шаблон соответствует логическому элементу И-НЕ:

В предыдущем разделе, там где мы разбираем «И-НЕ», этот тип вентиля был создан, когда мы взяли логический элемент И и усложнили его, добавив к выходу инвертор (элемент НЕ). Однако, если вникнуть в схему на рисунках 2-6, то увидим, что данная ТТЛ-конструкция – самый простой и естественный аппаратный способ реализовать функцию И-НЕ.

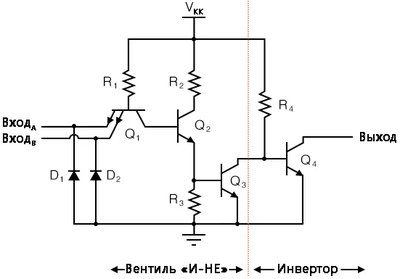

Чтобы реализовать функцию И с использованием ТТЛ-схемы, нужно немного усложнить эту схему, каскадно добавив к выходу инвертор, точно так же, как мы добавляли дополнительный транзисторный каскад в ТТЛ-схему инвертора, когда превращали его в «буфер»:

Вентиль «И»

Таблица истинности и эквивалентная схема (вентиль И-НЕ с инвертированным выходом) показаны здесь:

Само собой, схемы вентилей И-НЕ и ИЛИ можно спроектировать с каскадным выходом типа «тотемный столб», а не с выходом с открытым коллектором. Версии с выходом с открытым коллектором несколько проще, поэтому их я и предпочитаю использовать в качестве примеров.

Итог

- Вентиль И-НЕ можно создать, взяв ТТЛ-схему инвертора и добавив ещё один вход.

- Вентиль И можно создать, каскадно добавив инвертор к выходу в ТТЛ-схему вентиля И-НЕ.

См.также

Внешние ссылки

- Электроника

- Перевод:valemak

- Перевод от valemak

- Перевёл valemak

- Проверка:myagkij

- Оформление:myagkij

- Редактирование:myagkij

- Страницы, где используется шаблон "Навигационная таблица/Телепорт"

- Страницы с телепортом

- Цифровая электроника

- Логические вентили

- Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»

- Вентиль «И»

- Вентиль «И-НЕ»