Электроника:Цифровая электроника/Сдвиговые регистры/Сдвиговые регистры – Введение: различия между версиями

Valemak (обсуждение | вклад) |

Нет описания правки |

||

| (не показано 5 промежуточных версий 2 участников) | |||

| Строка 5: | Строка 5: | ||

=Сдвиговые регистры – Введение<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-12/introduction-to-shift-registers/ www.allaboutcircuits.com - Introduction to Shift Registers]</ref>= | =Сдвиговые регистры – Введение<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-12/introduction-to-shift-registers/ www.allaboutcircuits.com - Introduction to Shift Registers]</ref>= | ||

Сдвиговые регистры, как и | [[Сдвиговые регистры]], как и [[счётчик]]и, – это уже секвенциальная (она же последовательностная) логика. | ||

Последовательностная логика отличная от комбинационной тем, что на выход влияет не только текущий вход, но и предшествующие входы. | [[Последовательностная логика]] отличная от комбинационной тем, что на выход влияет не только текущий вход, но и предшествующие входы. | ||

Другими словами, последовательностная логика хранит в памяти историю прошлых входов. | Другими словами, [[последовательностная логика]] хранит в памяти историю прошлых входов. | ||

Сдвиговые регистры обеспечивают дискретную задержку цифрового сигнала или волны. | [[Сдвиговые регистры]] обеспечивают дискретную задержку цифрового сигнала или волны. | ||

Прямоугольная волна, синхронизированная с тактовым входом, задерживается на «n» дискретных тактовых импульсов, где «n» — количество этапов (шагов) сдвигового регистра. | Прямоугольная волна, синхронизированная с тактовым входом, задерживается на «n» дискретных тактовых импульсов, где «n» — количество этапов (шагов) [[сдвигового регистра]]. | ||

Таким образом, четырёхэтапный сдвиговый регистр задерживает «входные данные» на четыре такта, прежде чем выдаются «выходные данные». | Таким образом, [[четырёхэтапный сдвиговый регистр]] задерживает «входные данные» на четыре такта, прежде чем выдаются «выходные данные». | ||

Этапы в сдвиговом регистре представляют собой шаги задержки, обычно для этого используются D- или JK- | Этапы в сдвиговом регистре представляют собой шаги задержки, обычно для этого используются D- или [[JK-триггер]]ы. | ||

В старые добрые времена цифровой памятью служили очень длинные (до нескольких сотен разрядов) сдвиговые регистры. | В старые добрые времена цифровой памятью служили очень длинные (до нескольких сотен разрядов) [[сдвиговые регистры]]. | ||

Это устаревшее приложение напоминает акустические ртутные линии задержки, использовавшиеся на заре компьютерных технологий в качестве памяти. | Это устаревшее приложение напоминает акустические ртутные линии задержки, использовавшиеся на заре компьютерных технологий в качестве памяти. | ||

Последовательностная передача данных на расстояние от нескольких метров до километров использует сдвиговые регистры для преобразования параллельных данных в последовательностную форму. | Последовательностная передача данных на расстояние от нескольких метров до километров использует [[сдвиговые регистры]] для преобразования параллельных данных в последовательностную форму. | ||

Последовательностная передача данных заменяет множество медленных параллельных проводов одной последовательностной высокоскоростной схемой. | Последовательностная передача данных заменяет множество медленных параллельных проводов одной последовательностной высокоскоростной схемой. | ||

Секвенциальные данные на более коротких расстояниях (в десятки сантиметров) используют сдвиговые регистры для передачи данных в | Секвенциальные данные на более коротких расстояниях (в десятки сантиметров) используют [[сдвиговые регистры]] для передачи данных в [[микропроцессор]]ы и из них. | ||

Многочисленные периферийные устройства, в том числе аналого-цифровые преобразователи, цифро-аналоговые преобразователи, драйверы дисплея и память, используют сдвиговые регистры для уменьшения количества проводов на печатных платах. | Многочисленные периферийные устройства, в том числе [[аналого-цифровые преобразователи]], [[цифро-аналоговые преобразователи]], [[драйверы дисплея]] и [[память]], используют [[сдвиговые регистры]] для уменьшения количества проводов на печатных платах. | ||

Некоторые специализированные схемы счётчиков фактически используют сдвиговые регистры для генерации повторяющихся сигналов. | Некоторые специализированные схемы счётчиков фактически используют [[сдвиговые регистры]] для генерации повторяющихся сигналов. | ||

Более длинные сдвиговые регистры с помощью обратной связи генерируют паттерны настолько длинные, что выглядят как случайный шум (по сути – псевдошум). | Более длинные [[сдвиговые регистры]] с помощью обратной связи генерируют паттерны настолько длинные, что выглядят как случайный шум (по сути – псевдошум). | ||

По своей структуре базовые сдвиговые регистры классифицируются в соответствии со следующими типами: | По своей структуре базовые [[сдвиговые регистры]] классифицируются в соответствии со следующими типами: | ||

*Последовательный вход / последовательный выход (англ. ''SISO'' от '''''S'''erial-'''I'''n'' – '''''S'''erial-'''O'''ut'') | * Последовательный вход / последовательный выход (англ. ''[[SISO]]'' от '''''S'''erial-'''I'''n'' – '''''S'''erial-'''O'''ut'') | ||

*Параллельный вход / последовательный выход (англ. ''PISO'' от '''''P'''arallel-'''I'''n'' – '''''S'''erial-'''O'''ut'') | * Параллельный вход / последовательный выход (англ. ''[[PISO]]'' от '''''P'''arallel-'''I'''n'' – '''''S'''erial-'''O'''ut'') | ||

*Последовательный вход / параллельный выход (англ. ''SIPO'' от '''''S'''erial-'''I'''n'' – '''''P'''arallel-'''O'''ut'') | * Последовательный вход / параллельный выход (англ. ''[[SIPO]]'' от '''''S'''erial-'''I'''n'' – '''''P'''arallel-'''O'''ut'') | ||

*Универсальный сдвиговый регистр: параллельный вход / параллельный выход (англ. ''PIPO'' от '''''P'''arallel-'''I'''n'' – '''''P'''arallel-'''O'''ut'') | * Универсальный сдвиговый регистр: параллельный вход / параллельный выход (англ. ''[[PIPO]]'' от '''''P'''arallel-'''I'''n'' – '''''P'''arallel-'''O'''ut'') | ||

*Кольцевой счётчик | * [[Кольцевой счётчик]] | ||

== Последовательный вход / последовательный выход == | == Последовательный вход / последовательный выход == | ||

[[File:IV-12_1_1.png|500px|center|thumb|'''Рис. 1.''' 4-этапный сдвиговый регистр с последовательным входом и последовательным выходом.|alt=Рис. 1. 4-этапный сдвиговый регистр с последовательным входом и последовательным выходом.]] | [[File:IV-12_1_1.png|500px|center|thumb|'''Рис. 1.''' [[4-этапный сдвиговый регистр с последовательным входом и последовательным выходом]].|alt=Рис. 1. 4-этапный сдвиговый регистр с последовательным входом и последовательным выходом.]] | ||

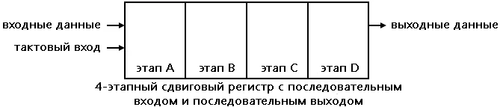

На рисунке 1 выше показана блок-схема сдвигового регистра с последовательным входом/выходом, состоящего из 4-х этапов. | На рисунке 1 выше показана блок-схема [[сдвигового регистра с последовательным входом/выходом]], состоящего из 4-х этапов. | ||

При получении входных данных будет произведена задержка на четыре такта после чего будут получены выходные данные сдвигового регистра. | При получении входных данных будет произведена задержка на четыре такта после чего будут получены выходные данные [[сдвигового регистра]]. | ||

Информация с узла «входные данные» передастся на выход этапа А после первого тактового импульса. После второго импульса эти же данные передаются на выход этапа В, а узел «входящие данные» передаёт на выход этапа А следующий пакет. После третьего тактового сигнала этап C принимает то, что ему передаст этап B; этап B получит данные из этапа A; а этап А принимает новую информацию из «входящих данных». | Информация с узла «входные данные» передастся на выход этапа А после первого тактового импульса. После второго импульса эти же данные передаются на выход этапа В, а узел «входящие данные» передаёт на выход этапа А следующий пакет. После третьего тактового сигнала этап C принимает то, что ему передаст этап B; этап B получит данные из этапа A; а этап А принимает новую информацию из «входящих данных». | ||

После | После четвёртого такта данные, первоначально представленные на «входных данных», окажутся на этапе D, это уже «выходные данные». | ||

Для данных выполняется принцип «первый вошёл → первый вышел», поскольку изначально загруженная информация первой мигрирует от «входных данных» к «выходным данным». | Для данных выполняется принцип «первый вошёл → первый вышел», поскольку изначально загруженная информация первой мигрирует от «входных данных» к «выходным данным». | ||

| Строка 58: | Строка 58: | ||

== Параллельный вход / последовательный выход == | == Параллельный вход / последовательный выход == | ||

[[File:IV-12_1_2.png|500px|center|thumb|'''Рис. 2.''' 4-этапный сдвиговый регистр с параллельным входом и последовательным выходом.|alt=Рис. 2. 4-этапный сдвиговый регистр с параллельным входом и последовательным выходом.]] | [[File:IV-12_1_2.png|500px|center|thumb|'''Рис. 2.''' [[4-этапный сдвиговый регистр с параллельным входом и последовательным выходом]].|alt=Рис. 2. 4-этапный сдвиговый регистр с параллельным входом и последовательным выходом.]] | ||

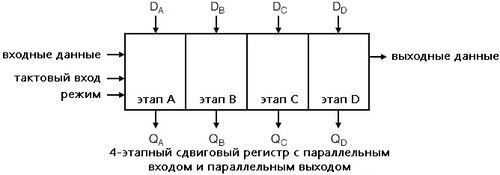

В этом случае данные загружаются одновременно во все этапы сдвигового регистра с параллельным входом и последовательным выходом. | В этом случае данные загружаются одновременно во все этапы [[сдвигового регистра с параллельным входом и последовательным выходом]]. | ||

Затем данные выводятся через узел «выходные данные» с помощью тактовых импульсов. Поскольку выше показан 4-этапный сдвиговый регистр, для сдвига всех данных по направлению к выходу требуется четыре тактовых импульса. | Затем данные выводятся через узел «выходные данные» с помощью тактовых импульсов. Поскольку выше показан [[4-этапный сдвиговый регистр]], для сдвига всех данных по направлению к выходу требуется четыре тактовых импульса. | ||

На приведённой выше диаграмме данные этапа D окажутся на «выходе данных» до первого тактового импульса; данные этапа C окажутся на «выходе данных» между первым и вторым тактовыми импульсами; данные этапа B – между вторым и третьим тактовыми импульсами; и данные этапа A – между третьим и четвёртым тактом. | На приведённой выше диаграмме данные этапа D окажутся на «выходе данных» до первого тактового импульса; данные этапа C окажутся на «выходе данных» между первым и вторым тактовыми импульсами; данные этапа B – между вторым и третьим тактовыми импульсами; и данные этапа A – между третьим и четвёртым тактом. | ||

После четвёртого тактового импульса последовательные биты, поступающие с узла «входные данные» будут появляться в «выходных данных» сдвигового регистра после задержки в четыре тактовых импульса. | После четвёртого тактового импульса последовательные биты, поступающие с узла «входные данные» будут появляться в «выходных данных» [[сдвигового регистра]] после задержки в четыре тактовых импульса. | ||

Если бы четыре переключателя были подключены к D<sub>A</sub>—D<sub>D</sub>, состояние можно было бы считать в микропроцессор, используя только один выход данных и выход синхронизации. | Если бы четыре переключателя были подключены к D<sub>A</sub>—D<sub>D</sub>, состояние можно было бы считать в [[микропроцессор]], используя только один выход данных и выход синхронизации. | ||

Поскольку для добавления дополнительных переключателей не потребуются дополнительные контакты, этот подход выглядит привлекательным в случае множественных входов. | Поскольку для добавления дополнительных переключателей не потребуются дополнительные контакты, этот подход выглядит привлекательным в случае множественных входов. | ||

| Строка 74: | Строка 74: | ||

== Последовательный вход / параллельный выход == | == Последовательный вход / параллельный выход == | ||

[[File:IV-12_1_3.png|500px|center|thumb|'''Рис. 3.''' 4-этапный сдвиговый регистр с последовательным входом и параллельным выходом. |alt=Рис. 3. 4-этапный сдвиговый регистр с последовательным входом и параллельным выходом. ]] | [[File:IV-12_1_3.png|500px|center|thumb|'''Рис. 3.''' [[4-этапный сдвиговый регистр с последовательным входом и параллельным выходом]]. |alt=Рис. 3. 4-этапный сдвиговый регистр с последовательным входом и параллельным выходом. ]] | ||

На рисунке 3 выше четыре бита данных будут смещены из «входных данных» на четыре тактовых импульса и будут доступны на Q<sub>A</sub>—Q<sub>D</sub> для управления внешними схемами ( | На рисунке 3 выше четыре бита данных будут смещены из «входных данных» на четыре тактовых импульса и будут доступны на Q<sub>A</sub>—Q<sub>D</sub> для управления внешними схемами ([[светодиод]]ы, лампы, [[драйверы реле]] и звуковые сигналы). После первых тактов информация из «входных данных» появляются в Q<sub>A</sub>. | ||

После второго такта старые данные Q<sub>A</sub> переходят в Q<sub>B</sub>; Q<sub>A</sub> получает следующие данные от узла «входные данные». После третьего такта данные Q<sub>B</sub> переходят в Q<sub>C</sub>. | После второго такта старые данные Q<sub>A</sub> переходят в Q<sub>B</sub>; Q<sub>A</sub> получает следующие данные от узла «входные данные». После третьего такта данные Q<sub>B</sub> переходят в Q<sub>C</sub>. | ||

После четвёртого такта данные Q<sub>C</sub> переходят в Q<sub>D</sub>. Теперь этот этап содержит те данные, что были впервые представленны на «входных данных». Сдвиговый регистр теперь должен содержать четыре бита данных. | После четвёртого такта данные Q<sub>C</sub> переходят в Q<sub>D</sub>. Теперь этот этап содержит те данные, что были впервые представленны на «входных данных». [[Сдвиговый регистр]] теперь должен содержать четыре бита данных. | ||

== Универсальный сдвиговый регистр: параллельный вход / параллельный выход == | == Универсальный сдвиговый регистр: параллельный вход / параллельный выход == | ||

[[File:IV-12_1_4.png|500px|center|thumb|'''Рис. 4.''' Универсальный вариант: 4-этапный сдвиговый регистр с параллельным входом и параллельным выходом.|alt=Рис. 4. Универсальный вариант: 4-этапный сдвиговый регистр с параллельным входом и параллельным выходом.]] | [[File:IV-12_1_4.png|500px|center|thumb|'''Рис. 4.''' Универсальный вариант: [[4-этапный сдвиговый регистр с параллельным входом и параллельным выходом]].|alt=Рис. 4. Универсальный вариант: 4-этапный сдвиговый регистр с параллельным входом и параллельным выходом.]] | ||

Сдвиговый регистр, у которого | [[Сдвиговый регистр]], у которого параллельны как вход, так и выход, сочетает в себе функциональность [[сдвигового регистра]] с параллельным входом и выходом с функциональностью [[сдвигового регистра с последовательным входом и параллельным выходом]], образуя [[универсальный сдвиговый регистр]]. | ||

Подобный переключатель а-ля «выполни как угодно» имеет свою цену – увеличенное количество контактов ввода/вывода (вход/выход) может уменьшить количество каскадов, которые могут быть упакованы. | Подобный переключатель а-ля «выполни как угодно» имеет свою цену – увеличенное количество контактов ввода/вывода (вход/выход) может уменьшить количество каскадов, которые могут быть упакованы. | ||

Данные, представленные в D<sub>A</sub>—D<sub>D</sub>, параллельно загружаются в | Данные, представленные в D<sub>A</sub>—D<sub>D</sub>, параллельно загружаются в [[регистр]]ы. | ||

Эти данные в Q<sub>A</sub>—Q<sub>D</sub> могут быть сдвинуты на то количество импульсов, что представлено на тактовом входе. | Эти данные в Q<sub>A</sub>—Q<sub>D</sub> могут быть сдвинуты на то количество импульсов, что представлено на тактовом входе. | ||

| Строка 102: | Строка 102: | ||

== Кольцевой счётчик == | == Кольцевой счётчик == | ||

[[File:IV-12_1_5.png|500px|center|thumb|'''Рис. 5.''' Сдвиговый регистр – кольцевой счётчик.|alt=Рис. 5. Сдвиговый регистр – кольцевой счётчик.]] | [[File:IV-12_1_5.png|500px|center|thumb|'''Рис. 5.''' [[Сдвиговый регистр]] – [[кольцевой счётчик]].|alt=Рис. 5. Сдвиговый регистр – кольцевой счётчик.]] | ||

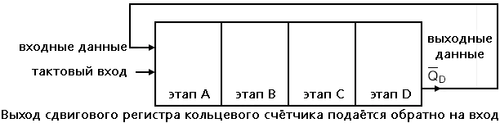

Если последовательный выход сдвигового регистра подключён к последовательному входу, круговорот одних и тех же данных может непрерывно происходить, пока имеют место тактовые импульсы. | Если последовательный выход [[сдвигового регистра]] подключён к последовательному входу, круговорот одних и тех же данных может непрерывно происходить, пока имеют место тактовые импульсы. | ||

Если выход инвертируется перед обратной связью, как показано на рисунке 5 выше, то нам не нужно беспокоиться о загрузке исходных данных в «кольцевой счётчик». | Если выход инвертируется перед обратной связью, как показано на рисунке 5 выше, то нам не нужно беспокоиться о загрузке исходных данных в «кольцевой счётчик». | ||

| Строка 110: | Строка 110: | ||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 116: | Строка 116: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника | {{Навигационная таблица/Портал/Электроника}} | ||

Текущая версия от 21:52, 22 мая 2023

Сдвиговые регистры – Введение[1]

Сдвиговые регистры, как и счётчики, – это уже секвенциальная (она же последовательностная) логика.

Последовательностная логика отличная от комбинационной тем, что на выход влияет не только текущий вход, но и предшествующие входы.

Другими словами, последовательностная логика хранит в памяти историю прошлых входов.

Сдвиговые регистры обеспечивают дискретную задержку цифрового сигнала или волны.

Прямоугольная волна, синхронизированная с тактовым входом, задерживается на «n» дискретных тактовых импульсов, где «n» — количество этапов (шагов) сдвигового регистра. Таким образом, четырёхэтапный сдвиговый регистр задерживает «входные данные» на четыре такта, прежде чем выдаются «выходные данные».

Этапы в сдвиговом регистре представляют собой шаги задержки, обычно для этого используются D- или JK-триггеры.

В старые добрые времена цифровой памятью служили очень длинные (до нескольких сотен разрядов) сдвиговые регистры.

Это устаревшее приложение напоминает акустические ртутные линии задержки, использовавшиеся на заре компьютерных технологий в качестве памяти.

Последовательностная передача данных на расстояние от нескольких метров до километров использует сдвиговые регистры для преобразования параллельных данных в последовательностную форму.

Последовательностная передача данных заменяет множество медленных параллельных проводов одной последовательностной высокоскоростной схемой.

Секвенциальные данные на более коротких расстояниях (в десятки сантиметров) используют сдвиговые регистры для передачи данных в микропроцессоры и из них.

Многочисленные периферийные устройства, в том числе аналого-цифровые преобразователи, цифро-аналоговые преобразователи, драйверы дисплея и память, используют сдвиговые регистры для уменьшения количества проводов на печатных платах.

Некоторые специализированные схемы счётчиков фактически используют сдвиговые регистры для генерации повторяющихся сигналов.

Более длинные сдвиговые регистры с помощью обратной связи генерируют паттерны настолько длинные, что выглядят как случайный шум (по сути – псевдошум).

По своей структуре базовые сдвиговые регистры классифицируются в соответствии со следующими типами:

- Последовательный вход / последовательный выход (англ. SISO от Serial-In – Serial-Out)

- Параллельный вход / последовательный выход (англ. PISO от Parallel-In – Serial-Out)

- Последовательный вход / параллельный выход (англ. SIPO от Serial-In – Parallel-Out)

- Универсальный сдвиговый регистр: параллельный вход / параллельный выход (англ. PIPO от Parallel-In – Parallel-Out)

- Кольцевой счётчик

Последовательный вход / последовательный выход

На рисунке 1 выше показана блок-схема сдвигового регистра с последовательным входом/выходом, состоящего из 4-х этапов.

При получении входных данных будет произведена задержка на четыре такта после чего будут получены выходные данные сдвигового регистра.

Информация с узла «входные данные» передастся на выход этапа А после первого тактового импульса. После второго импульса эти же данные передаются на выход этапа В, а узел «входящие данные» передаёт на выход этапа А следующий пакет. После третьего тактового сигнала этап C принимает то, что ему передаст этап B; этап B получит данные из этапа A; а этап А принимает новую информацию из «входящих данных».

После четвёртого такта данные, первоначально представленные на «входных данных», окажутся на этапе D, это уже «выходные данные».

Для данных выполняется принцип «первый вошёл → первый вышел», поскольку изначально загруженная информация первой мигрирует от «входных данных» к «выходным данным».

Параллельный вход / последовательный выход

В этом случае данные загружаются одновременно во все этапы сдвигового регистра с параллельным входом и последовательным выходом.

Затем данные выводятся через узел «выходные данные» с помощью тактовых импульсов. Поскольку выше показан 4-этапный сдвиговый регистр, для сдвига всех данных по направлению к выходу требуется четыре тактовых импульса.

На приведённой выше диаграмме данные этапа D окажутся на «выходе данных» до первого тактового импульса; данные этапа C окажутся на «выходе данных» между первым и вторым тактовыми импульсами; данные этапа B – между вторым и третьим тактовыми импульсами; и данные этапа A – между третьим и четвёртым тактом.

После четвёртого тактового импульса последовательные биты, поступающие с узла «входные данные» будут появляться в «выходных данных» сдвигового регистра после задержки в четыре тактовых импульса.

Если бы четыре переключателя были подключены к DA—DD, состояние можно было бы считать в микропроцессор, используя только один выход данных и выход синхронизации.

Поскольку для добавления дополнительных переключателей не потребуются дополнительные контакты, этот подход выглядит привлекательным в случае множественных входов.

Последовательный вход / параллельный выход

На рисунке 3 выше четыре бита данных будут смещены из «входных данных» на четыре тактовых импульса и будут доступны на QA—QD для управления внешними схемами (светодиоды, лампы, драйверы реле и звуковые сигналы). После первых тактов информация из «входных данных» появляются в QA.

После второго такта старые данные QA переходят в QB; QA получает следующие данные от узла «входные данные». После третьего такта данные QB переходят в QC.

После четвёртого такта данные QC переходят в QD. Теперь этот этап содержит те данные, что были впервые представленны на «входных данных». Сдвиговый регистр теперь должен содержать четыре бита данных.

Универсальный сдвиговый регистр: параллельный вход / параллельный выход

Сдвиговый регистр, у которого параллельны как вход, так и выход, сочетает в себе функциональность сдвигового регистра с параллельным входом и выходом с функциональностью сдвигового регистра с последовательным входом и параллельным выходом, образуя универсальный сдвиговый регистр.

Подобный переключатель а-ля «выполни как угодно» имеет свою цену – увеличенное количество контактов ввода/вывода (вход/выход) может уменьшить количество каскадов, которые могут быть упакованы.

Данные, представленные в DA—DD, параллельно загружаются в регистры.

Эти данные в QA—QD могут быть сдвинуты на то количество импульсов, что представлено на тактовом входе.

Сдвинутые данные доступны на QA—QD.

Вход «режим» (который может быть представлен более чем одним входом), управляет параллельной загрузкой данных от DA до DD, смещением данных и направлением сдвига.

Есть также регистры сдвига, сдвигающие данные влево или вправо.

Кольцевой счётчик

Если последовательный выход сдвигового регистра подключён к последовательному входу, круговорот одних и тех же данных может непрерывно происходить, пока имеют место тактовые импульсы.

Если выход инвертируется перед обратной связью, как показано на рисунке 5 выше, то нам не нужно беспокоиться о загрузке исходных данных в «кольцевой счётчик».

См.также

Внешние ссылки