Электроника:Цифровая электроника/Сдвиговые регистры/Сдвиговые регистры: последовательный вход, последовательный выход (SISO): различия между версиями

Valemak (обсуждение | вклад) (Новая страница: «{{Панель управления/Электроника}} {{Перевод от valemak}} {{Myagkij-редактор}} =Сдвиговые регистры:...») |

Нет описания правки |

||

| (не показано 5 промежуточных версий 2 участников) | |||

| Строка 5: | Строка 5: | ||

=Сдвиговые регистры: последовательный вход, последовательный выход (SISO)<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-12/serial-in-serial-out-shift-register/ www.allaboutcircuits.com - Shift Registers: Serial-in, Serial-out]</ref>= | =Сдвиговые регистры: последовательный вход, последовательный выход (SISO)<ref>[https://www.allaboutcircuits.com/textbook/digital/chpt-12/serial-in-serial-out-shift-register/ www.allaboutcircuits.com - Shift Registers: Serial-in, Serial-out]</ref>= | ||

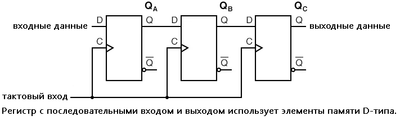

Сдвиговые регистры с последовательным вводом и выводом задерживают данные на один такт для каждого этапа. | [[Сдвиговые регистры с последовательным вводом и выводом]] задерживают данные на один такт для каждого этапа. | ||

Они хранят бит данных в каждом | Они хранят бит данных в каждом [[регистр]]е. [[Сдвиговый регистр с последовательными входом и выходом]] обычно имеют длину от одного до 64 бит (но можно и больше), если [[регистр]]ы или пакеты каскадируются. | ||

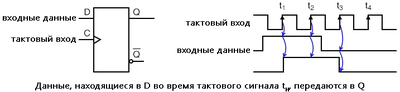

Ниже показан одноэтапный сдвиговый регистр, принимающий данные, которые не синхронизированы с тактовым входом | Ниже показан одноэтапный [[сдвиговый регистр]], принимающий данные, которые не синхронизированы с тактовым входом [[регистр]]а. | ||

«Входные данных» на терминале типа «D» (D- | «Входные данных» на терминале типа «D» ([[D-триггер]]е) не меняет уровни, когда тактовый сигнал меняется с «низкого» на «высокий». | ||

Мы можем захотеть синхронизировать данные с общесистемными часами на печатной плате, чтобы повысить надёжность цифровой логической схемы. | Мы можем захотеть синхронизировать данные с общесистемными часами на печатной плате, чтобы повысить надёжность цифровой логической схемы. | ||

[[File:IV-12_2_1.png|400px|center|thumb|Рис. 1. «Входные данные» на терминале типа «D» (D- | [[File:IV-12_2_1.png|400px|center|thumb|'''Рис. 1.''' «Входные данные» на терминале типа «D» ([[D-триггер]]е) не изменяет уровни.|alt=Рис. 1. «Входные данные» на терминале типа «D» (D-триггере) не изменяет уровни.]] | ||

Очевидный момент (по сравнению с рисунком 2 ниже), показанный на рисунке 1 выше, заключается в том, что любые «входные данные», присутствующие на терминале типа «D», передаются с D на выход Q за тактовое время. | Очевидный момент (по сравнению с рисунком 2 ниже), показанный на рисунке 1 выше, заключается в том, что любые «входные данные», присутствующие на терминале типа «D», передаются с D на выход Q за тактовое время. | ||

Поскольку в нашем примере сдвиговый регистр использует элементы памяти, чувствительные к положительному фронту, выход Q следует за входом D, когда тактовый сигнал переходит от «низкого» уровня к «высокому», как показано стрелками вверх на рисунке 1 выше. | Поскольку в нашем примере [[сдвиговый регистр]] использует элементы памяти, чувствительные к положительному фронту, выход Q следует за входом D, когда тактовый сигнал переходит от «низкого» уровня к «высокому», как показано стрелками вверх на рисунке 1 выше. | ||

Несомненно, такой логический уровень присутствует во время тактового сигнала, потому что данные стабильны задолго до и после фронта тактового сигнала. | Несомненно, такой логический уровень присутствует во время тактового сигнала, потому что данные стабильны задолго до и после фронта тактового сигнала. | ||

| Строка 35: | Строка 35: | ||

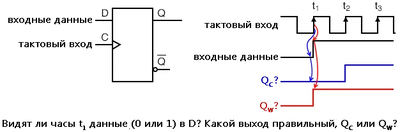

Если кратенько, то он воспринимает данные, которые присутствовали в точке D до тактового сигнала. | Если кратенько, то он воспринимает данные, которые присутствовали в точке D до тактового сигнала. | ||

Это то, что передаётся в Q в момент времени t1. Правильная волна на рисунке 2 – это | Это то, что передаётся в Q в момент времени t1. Правильная волна на рисунке 2 – это Q<sub>C</sub>. В момент t<sub>1</sub> Q обращается в нуль, если он уже не равен нулю. | ||

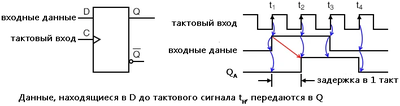

Регистр D не «видит» единицу до момента t<sub>2</sub>, когда Q становится «высоким». | [[Регистр]] D не «видит» единицу до момента t<sub>2</sub>, когда Q становится «высоким». | ||

[[File:IV-12_2_3.png|400px|center|thumb|'''Рис. 3.''' Регистр D не «видит» единицу до момента t<sub>2</sub>, когда Q становится «высоким».|alt=Рис. 3. Регистр D не «видит» единицу до момента t2, когда Q становится «высоким».]] | [[File:IV-12_2_3.png|400px|center|thumb|'''Рис. 3.''' Регистр D не «видит» единицу до момента t<sub>2</sub>, когда Q становится «высоким».|alt=Рис. 3. Регистр D не «видит» единицу до момента t2, когда Q становится «высоким».]] | ||

Поскольку данные, указанные выше, присутствующие в D, синхронизируются с Q за тактовое время, а Q не может измениться до следующего такта, D-триггер задерживает данные на один тактовый период при условии, что данные уже синхронизированы с таковым входом. Волна Q<sub>A</sub> такая же, как и для «входных данных» с задержкой в один тактовый период. | Поскольку данные, указанные выше, присутствующие в D, синхронизируются с Q за тактовое время, а Q не может измениться до следующего такта, [[D-триггер]] задерживает данные на один тактовый период при условии, что данные уже синхронизированы с таковым входом. Волна Q<sub>A</sub> такая же, как и для «входных данных» с задержкой в один тактовый период. | ||

Далее следует более подробный взгляд на то, что «видит» вход | Далее следует более подробный взгляд на то, что «видит» вход [[триггер]]а типа D за тактовое время. | ||

См. рисунок 4 ниже. Поскольку «входные данные» меняются во времени (как на рисунке 3 выше), нам нужна дополнительная информация, чтобы определить, что именно «видит» D-триггер. | См. рисунок 4 ниже. Поскольку «входные данные» меняются во времени (как на рисунке 3 выше), нам нужна дополнительная информация, чтобы определить, что именно «видит» D-триггер. | ||

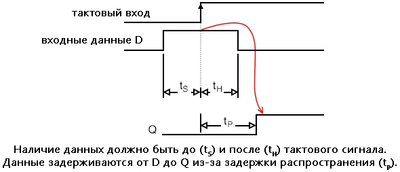

Если «входные данные» поступают из другого этапа сдвигового регистра, другого типа D- | Если «входные данные» поступают из другого этапа сдвигового регистра, другого типа [[D-триггер]]а, мы можем сделать некоторые выводы на основе информации из таблицы данных. | ||

Производители цифровой логики предоставляют информацию о своих деталях в виде таблиц, которые ранее были доступны только в сборнике, называемом справочником данных. | Производители цифровой логики предоставляют информацию о своих деталях в виде таблиц, которые ранее были доступны только в сборнике, называемом справочником данных. | ||

| Строка 55: | Строка 55: | ||

[[File:IV-12_2_4.png|400px|center|thumb|'''Рис. 4.''' В наши дни информацию о деталях лучше всего брать с веб-сайта производителя.|alt=Рис. 4. В наши дни информацию о деталях лучше всего брать с веб-сайта производителя.]] | [[File:IV-12_2_4.png|400px|center|thumb|'''Рис. 4.''' В наши дни информацию о деталях лучше всего брать с веб-сайта производителя.|alt=Рис. 4. В наши дни информацию о деталях лучше всего брать с веб-сайта производителя.]] | ||

Следующие данные были взяты из технического описания CD4006b для работы при напряжении 5 В постоянного тока и служат в качестве примера для иллюстрации синхронизации. | Следующие данные были взяты из технического описания [[CD4006b]] для работы при напряжении 5 В постоянного тока и служат в качестве примера для иллюстрации синхронизации. | ||

*t<sub>S</sub> = 100 нс | *t<sub>S</sub> = 100 нс | ||

| Строка 65: | Строка 65: | ||

Кроме того, данные должны храниться в течение времени удержания t<sub>H</sub> = 60 нс после тактового импульса. Эти два условия должны быть выполнены для надёжной синхронизации данных от D до Q триггера. | Кроме того, данные должны храниться в течение времени удержания t<sub>H</sub> = 60 нс после тактового импульса. Эти два условия должны быть выполнены для надёжной синхронизации данных от D до Q триггера. | ||

С соблюдением времени установки 60 нс проблем не возникает, так как данные в D были там в течение всего предыдущего тактового периода, раз уж они поступают из другого этапа сдвигового регистра. | С соблюдением времени установки 60 нс проблем не возникает, так как данные в D были там в течение всего предыдущего тактового периода, раз уж они поступают из другого этапа [[сдвигового регистра]]. | ||

Например, при тактовой частоте 1 МГц тактовый период составляет 1000 мкс, это достаточно много времени. | Например, при тактовой частоте 1 МГц тактовый период составляет 1000 мкс, это достаточно много времени. | ||

| Строка 71: | Строка 71: | ||

Фактически данные будут присутствовать за 1000 мкс до тактового сигнала, что намного больше минимального требуемого t<sub>S</sub> в 60 нс. | Фактически данные будут присутствовать за 1000 мкс до тактового сигнала, что намного больше минимального требуемого t<sub>S</sub> в 60 нс. | ||

Время удержания t<sub>H</sub> = 60 нс соблюдается, поскольку D, подключённый к Q другого каскада, не может изменяться быстрее, чем задержка распространения предыдущего | Время удержания t<sub>H</sub> = 60 нс соблюдается, поскольку D, подключённый к Q другого каскада, не может изменяться быстрее, чем задержка распространения предыдущего [[каскад]]а t<sub>P</sub> = 200 нс. | ||

Время удержания сохраняется до тех пор, пока задержка распространения предыдущего D- | Время удержания сохраняется до тех пор, пока задержка распространения предыдущего [[D-триггер]]а больше, чем это самое время удержания. | ||

Данные в D, управляемые другим каскадом Q, не будут изменяться быстрее, чем за 200 нс для CD4006b. | Данные в D, управляемые другим каскадом Q, не будут изменяться быстрее, чем за 200 нс для [[CD4006b]]. | ||

Подводя итог, можно сказать, что выход Q следует за входом D примерно по тактовой частоте, если триггеры каскадированы в многоэтапный сдвиговый регистр. | Подводя итог, можно сказать, что выход Q следует за входом D примерно по тактовой частоте, если триггеры каскадированы в [[многоэтапный сдвиговый регистр]]. | ||

[[File:IV-12_2_5.png|400px|center|thumb|'''Рис. 5.''' Выход Q следует за входом D почти по тактам, если | [[File:IV-12_2_5.png|400px|center|thumb|'''Рис. 5.''' Выход Q следует за входом D почти по тактам, если [[триггер]]ы каскадированы в [[многоэтапный сдвиговый регистр]].|alt=Рис. 5. Выход Q следует за входом D почти по тактам, если триггеры каскадированы в многоэтапный сдвиговый регистр.]] | ||

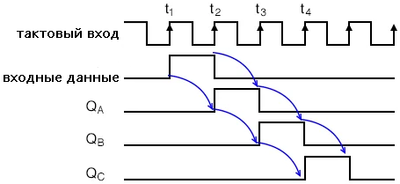

Три триггера типа «D» соединены каскадом от Q к D, а тактовые импульсы соединены параллельно, образуя трёхкаскадный сдвиговый регистр. | Три триггера типа «D» соединены каскадом от Q к D, а тактовые импульсы соединены параллельно, образуя [[трёхкаскадный сдвиговый регистр]]. | ||

[[File:IV-12_2_6.png|400px|center|thumb|'''Рис. 6.''' Три D- | [[File:IV-12_2_6.png|400px|center|thumb|'''Рис. 6.''' Три [[D-триггер]]а типа «D» соединённые в [[трёхкаскадный сдвиговый регистр]].|alt=Рис. 6. Три D-триггера типа «D» соединённые в трёхкаскадный сдвиговый регистр.]] | ||

JK- | [[JK-регистр]]ы формируют каскады Q в J, Q' в K с параллельными тактовыми импульсами, в результате чего получается альтернативная форма [[сдвигового регистра]], описанная выше. | ||

Сдвиговый регистр с последовательными входом и выходом имеет тактовый вход, ввод данных и вывод данных из последнего этапа. | [[Сдвиговый регистр с последовательными входом и выходом]] имеет тактовый вход, ввод данных и вывод данных из последнего этапа. | ||

Как правило, другие выходы | Как правило, другие выходы [[каскад]]а недоступны. В противном случае это был бы [[сдвиговый регистр с последовательным входом и параллельным выходом]]. | ||

Приведённые на рисунке 7 ниже волны сигналов относятся к любой из двух предыдущих версий сдвигового регистра с последовательными входом и выходом. | Приведённые на рисунке 7 ниже волны сигналов относятся к любой из двух предыдущих версий [[сдвигового регистра с последовательными входом и выходом]]. | ||

Три пары стрелок показывают, что трёхступенчатый сдвиговый регистр временно хранит 3 бита данных и задерживает их на три такта от ввода до вывода. | Три пары стрелок показывают, что [[трёхступенчатый сдвиговый регистр]] временно хранит 3 бита данных и задерживает их на три такта от ввода до вывода. | ||

[[File:IV-12_2_7.png|400px|center|thumb|'''Рис. 7.''' Одна из двух предыдущих версий сдвигового регистра с последовательным входом и выходом.|alt=Рис. 7. Одна из двух предыдущих версий сдвигового регистра с последовательным входом и выходом.]] | [[File:IV-12_2_7.png|400px|center|thumb|'''Рис. 7.''' Одна из двух предыдущих версий [[сдвигового регистра с последовательным входом и выходом]].|alt=Рис. 7. Одна из двух предыдущих версий сдвигового регистра с последовательным входом и выходом.]] | ||

В тактовое время t<sub>1</sub> нули на «входных данных» синхронизируются от D до Q всех трёх этапов. В частности, D этапа A «видит» логический 0, который синхронизируется с Q<sub>A</sub>, где он остаётся до момента времени t<sub>2</sub>. | В тактовое время t<sub>1</sub> нули на «входных данных» синхронизируются от D до Q всех трёх этапов. В частности, D этапа A «видит» логический 0, который синхронизируется с Q<sub>A</sub>, где он остаётся до момента времени t<sub>2</sub>. | ||

| Строка 101: | Строка 101: | ||

В тактовое время t<sub>2</sub> единицы на «входных данных» синхронизируется от D до Q<sub>A</sub>. На стадиях B и C нули, поступающие с предыдущих стадий, синхронизируется с Q<sub>B</sub> и Q<sub>C</sub>. | В тактовое время t<sub>2</sub> единицы на «входных данных» синхронизируется от D до Q<sub>A</sub>. На стадиях B и C нули, поступающие с предыдущих стадий, синхронизируется с Q<sub>B</sub> и Q<sub>C</sub>. | ||

В тактовое время | В тактовое время t<sub>3</sub> нули на «входных данных» синхронизируются от D до Q<sub>A</sub>. Q<sub>A</sub> становится «низким» и остаётся таковым для оставшихся тактов из-за того, что «входные данные» равны 0. Q<sub>B</sub> становится «высоким» в момент t<sub>3</sub> из-за 1 на предыдущем этапе. Q<sub>C</sub> всё ещё остаётся «низким» после t<sub>3</sub> из-за «низкого» уровня на предыдущем этапе. | ||

Q<sub>C</sub>, наконец, становится «высоким» на такте t<sub>4</sub> из-за «высокого» уровня, подаваемого на D с предыдущего этапа Q<sub>B</sub>. Всё более ранние этапы имеют смещенные в них 0. И после следующего тактового импульса в момент t<sub>5</sub> все логические единицы будут смещены и заменены на нули. | Q<sub>C</sub>, наконец, становится «высоким» на такте t<sub>4</sub> из-за «высокого» уровня, подаваемого на D с предыдущего этапа Q<sub>B</sub>. Всё более ранние этапы имеют смещенные в них 0. И после следующего тактового импульса в момент t<sub>5</sub> все логические единицы будут смещены и заменены на нули. | ||

| Строка 111: | Строка 111: | ||

Для получения полных спецификаций на сайте компании нужно открыть страницы таких устройств. | Для получения полных спецификаций на сайте компании нужно открыть страницы таких устройств. | ||

*CD4006b 18-битный сдвиговый регистр с последовательным входом/выходом. | * [[CD4006b]] 18-битный сдвиговый регистр с последовательным входом/выходом. | ||

*CD4031b 64-битный сдвиговый регистр с последовательным входом/выходом. | * [[CD4031b]] 64-битный сдвиговый регистр с последовательным входом/выходом. | ||

*CD4517b двойной 64-битный сдвиговый регистр с последовательным входом/выходом. | * [[CD4517b]] двойной 64-битный сдвиговый регистр с последовательным входом/выходом. | ||

Следующие регистры сдвига с последовательным входом/выходом относятся к семейству КМОП (комплементарных металлооксидных полупроводников) серии 4000. | Следующие [[регистры сдвига с последовательным входом/выходом]] относятся к семейству [[КМОП]] (комплементарных металлооксидных полупроводников) серии 4000. | ||

Таким образом, они будут принимать V<sub>DD</sub>, положительный источник питания от 3 до 15 вольт. Вывод V<sub>SS</sub> заземлён. | Таким образом, они будут принимать V<sub>DD</sub>, положительный источник питания от 3 до 15 вольт. Вывод V<sub>SS</sub> заземлён. | ||

| Строка 123: | Строка 123: | ||

[[File:IV-12_2_8.png|400px|center|thumb|'''Рис. 8.''' Максимальная частота часов сдвига, которая зависит от V<sub>DD</sub>, составляет несколько мегагерц. |alt=Рис. 8. Максимальная частота часов сдвига, которая зависит от VDD, составляет несколько мегагерц. ]] | [[File:IV-12_2_8.png|400px|center|thumb|'''Рис. 8.''' Максимальная частота часов сдвига, которая зависит от V<sub>DD</sub>, составляет несколько мегагерц. |alt=Рис. 8. Максимальная частота часов сдвига, которая зависит от VDD, составляет несколько мегагерц. ]] | ||

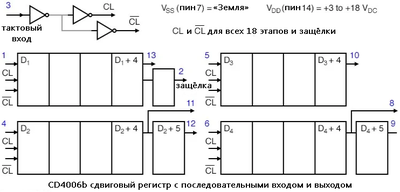

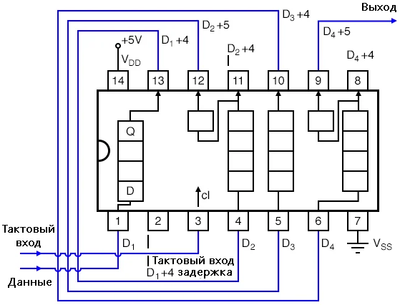

18-битный CD4006b состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита. | 18-битный [[CD4006b]] состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита. | ||

Таким образом, 5-битные ступени можно использовать как 4-битные сдвиговые регистры. | Таким образом, 5-битные ступени можно использовать как 4-битные сдвиговые регистры. | ||

Чтобы получить полный 18-битный сдвиговый регистр, выход одного сдвигового регистра должен быть каскадирован на вход другого и так далее, пока все каскады не создадут один сдвиговый регистр, как показано на рисунке 9 ниже. | Чтобы получить полный [[18-битный сдвиговый регистр]], выход одного сдвигового регистра должен быть каскадирован на вход другого и так далее, пока все каскады не создадут один сдвиговый регистр, как показано на рисунке 9 ниже. | ||

18-битный CD4006b состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита. | 18-битный [[CD4006b]] состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита. | ||

[[File:IV-12_2_9.png|400px|center|thumb|'''Рис. 9.''' 18-битный CD4006b.|alt=Рис. 9. 18-битный CD4006b.]] | [[File:IV-12_2_9.png|400px|center|thumb|'''Рис. 9.''' 18-битный [[CD4006b]].|alt=Рис. 9. 18-битный CD4006b.]] | ||

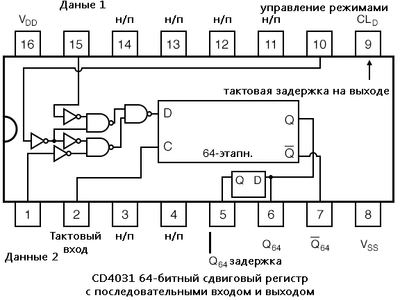

64-битный сдвиговый регистр последовательного ввода/вывода CD4031 показан ниже. | 64-битный сдвиговый регистр последовательного ввода/вывода [[CD4031]] показан ниже. | ||

Ряд контактов не подключены (отмечено как «н/п», т.е. нет подключения). И Q, и Q' доступны с 64-го этапа, на самом деле это | Ряд контактов не подключены (отмечено как «н/п», т.е. нет подключения). И Q, и Q' доступны с 64-го этапа, на самом деле это Q<sub>64</sub> и Q'<sub>64</sub>. | ||

Существует также Q<sub>64</sub>, «отстоящий» на пол-этапа, который задерживается на половину тактового цикла. Основной особенностью является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр. | Существует также Q<sub>64</sub>, «отстоящий» на пол-этапа, который задерживается на половину тактового цикла. Основной особенностью является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр. | ||

[[File:IV-12_2_10.png|400px|center|thumb|'''Рис. 10.''' Основной особенностью CD4031 является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр.|alt=Рис. 10. Основной особенностью CD4031 является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр.]] | [[File:IV-12_2_10.png|400px|center|thumb|'''Рис. 10.''' Основной особенностью [[CD4031]] является селекторный переключатель данных, который находится на входе данных в [[сдвиговый регистр]].|alt=Рис. 10. Основной особенностью CD4031 является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр.]] | ||

«Управление режимом» выбирает между двумя входами: «Данные 1» или «Данные 2». Если «управление режимом» имеет «высокий» уровень, данные будут выбраны из «Данные 2» для входа в сдвиговый регистр. | «Управление режимом» выбирает между двумя входами: «Данные 1» или «Данные 2». Если «управление режимом» имеет «высокий» уровень, данные будут выбраны из «Данные 2» для входа в [[сдвиговый регистр]]. | ||

В случае, когда «управление режимом» имеет «низкий» логический уровень, выбирается «Данные 1». Примеры этого показаны на двух рисунках ниже. | В случае, когда «управление режимом» имеет «низкий» логический уровень, выбирается «Данные 1». Примеры этого показаны на двух рисунках ниже. | ||

| Строка 147: | Строка 147: | ||

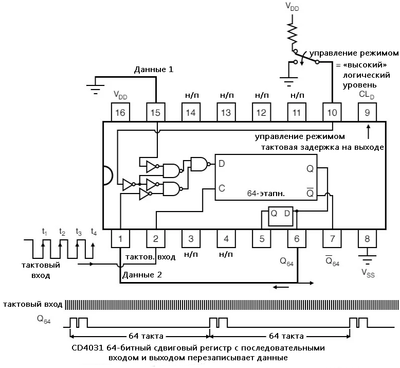

[[File:IV-12_2_11.png|400px|center|thumb|'''Рис. 11.''' «Управление режимом» выбирает между двумя входами: «Данные 1» и «Данные 2».|alt=Рис. 11. «Управление режимом» выбирает между двумя входами: «Данные 1» и «Данные 2».]] | [[File:IV-12_2_11.png|400px|center|thumb|'''Рис. 11.''' «Управление режимом» выбирает между двумя входами: «Данные 1» и «Данные 2».|alt=Рис. 11. «Управление режимом» выбирает между двумя входами: «Данные 1» и «Данные 2».]] | ||

«Данные 2» на рисунке 11 выше подключены к выходу Q<sub>64</sub> сдвигового регистра. При «высоком» уровне «управления режимом» выход Q<sub>64</sub> направляется обратно на вход данных D-переключателя. | «Данные 2» на рисунке 11 выше подключены к выходу Q<sub>64</sub> [[сдвигового регистра]]. При «высоком» уровне «управления режимом» выход Q<sub>64</sub> направляется обратно на вход данных D-переключателя. | ||

Данные будут циркулировать от вывода к вводу. Они будут повторяться каждые 64 тактовых импульса, как показано на рисунке 11 выше. | Данные будут циркулировать от вывода к вводу. Они будут повторяться каждые 64 тактовых импульса, как показано на рисунке 11 выше. | ||

Возникает вопрос: как этот шаблон данных вообще попал в сдвиговый регистр? | Возникает вопрос: как этот шаблон данных вообще попал в [[сдвиговый регистр]]? | ||

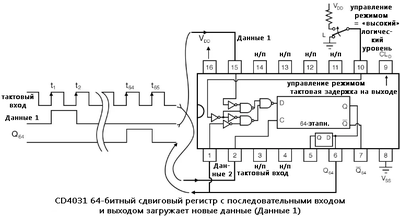

[[File:IV-12_2_12.png|400px|center|thumb|'''Рис. 12.''' При «низком» уровне «управления режимом» CD4031 «Данные 1» выбираются для ввода в переключатель.|alt=Рис. 12. При «низком» уровне «управления режимом» CD4031 «Данные 1» выбираются для ввода в переключатель.]] | [[File:IV-12_2_12.png|400px|center|thumb|'''Рис. 12.''' При «низком» уровне «управления режимом» [[CD4031]] «Данные 1» выбираются для ввода в переключатель.|alt=Рис. 12. При «низком» уровне «управления режимом» CD4031 «Данные 1» выбираются для ввода в переключатель.]] | ||

Выходной сигнал | Выходной сигнал Q<sub>64</sub> не рециркулируется, поскольку «нижний» вентиль селектора данных отключён. | ||

Под отключением мы подразумеваем, что «низкий» логический уровень «управления режимом», дважды инвертированный в «низкий» уровень на нижнем вентиле И-НЕ, предотвращает передачу любого сигнала на нижний контакт (Данные 2) на выход вентиля. | Под отключением мы подразумеваем, что «низкий» логический уровень «управления режимом», дважды инвертированный в «низкий» уровень на нижнем [[вентиле И-НЕ]], предотвращает передачу любого сигнала на нижний контакт (Данные 2) на выход вентиля. | ||

Таким образом, он отключён. | Таким образом, он отключён. | ||

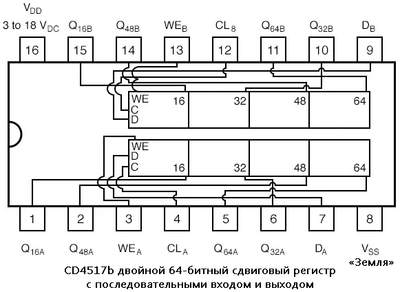

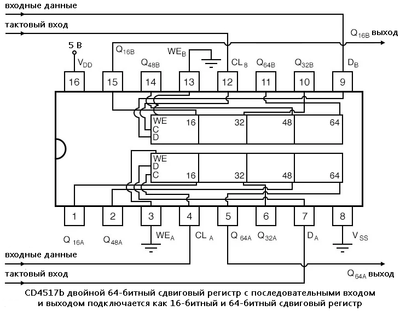

[[File:IV-12_2_13.png|400px|center|thumb|'''Рис. 13.''' При низком уровне «управления режимом» CD4517b «Данные 1» выбираются для ввода в переключатель.|alt=Рис. 13. При низком уровне «управления режимом» CD4517b «Данные 1» выбираются для ввода в переключатель.]] | [[File:IV-12_2_13.png|400px|center|thumb|'''Рис. 13.''' При низком уровне «управления режимом» [[CD4517b]] «Данные 1» выбираются для ввода в переключатель.|alt=Рис. 13. При низком уровне «управления режимом» CD4517b «Данные 1» выбираются для ввода в переключатель.]] | ||

Двойной 64-битный сдвиговый регистр CD4517b показан на рисунке 13 выше. Обратите внимание на отводы на 16-й, 32-й и 48-й этапах. | Двойной 64-битный сдвиговый регистр [[CD4517b]] показан на рисунке 13 выше. Обратите внимание на отводы на 16-й, 32-й и 48-й этапах. | ||

Сие значит, что сдвиговые регистры такой длины можно сконфигурировать из одного из 64-битных сдвиговых регистров. | Сие значит, что сдвиговые регистры такой длины можно сконфигурировать из одного из 64-битных сдвиговых регистров. | ||

| Строка 175: | Строка 175: | ||

Предположим, что нам требуется 16-битный регистр сдвига. | Предположим, что нам требуется 16-битный регистр сдвига. | ||

Можно ли это настроить с помощью CD4517b? Как насчёт 64-сдвигового регистра из той же части? | Можно ли это настроить с помощью [[CD4517b]]? Как насчёт 64-сдвигового регистра из той же части? | ||

[[File:IV-12_2_14.png|400px|center|thumb|'''Рис. 14.''' CD4517b подключается и как 16- так и 64-битный сдвиговый регистр.|alt=Рис. 14. CD4517b подключается и как 16- так и 64-битный сдвиговый регистр.]] | [[File:IV-12_2_14.png|400px|center|thumb|'''Рис. 14.''' [[CD4517b]] подключается и как 16- так и 64-битный сдвиговый регистр.|alt=Рис. 14. CD4517b подключается и как 16- так и 64-битный сдвиговый регистр.]] | ||

На рисунке 14 выше мы показываем A для CD4517b, подключённый как 16-битный регистр сдвига для секции B. | На рисунке 14 выше мы показываем A для [[CD4517b]], подключённый как 16-битный регистр сдвига для секции B. | ||

Тактовый вход этапа B – это CL<sub>B</sub>. Здесь данные синхронизируются. А данные, задержанные на 16 тактов, снимаются Q<sub>16B</sub>. WE<sub>B</sub>, разрешающая запись, заземлено. | Тактовый вход этапа B – это CL<sub>B</sub>. Здесь данные синхронизируются. А данные, задержанные на 16 тактов, снимаются Q<sub>16B</sub>. WE<sub>B</sub>, разрешающая запись, заземлено. | ||

Выше мы также показываем тот же CD4517b, подключённый в качестве 64-битного сдвигового регистра для независимой секции A. | Выше мы также показываем тот же [[CD4517b]], подключённый в качестве 64-битного сдвигового регистра для независимой секции A. | ||

Тактовый вход для секции A – это CL<sub>A</sub>. Данные поступают в CL<sub>A</sub>. Данные, задержанные на 64-тактовые импульсы, берутся из Q<sub>64A</sub>. WE<sub>A</sub>, разрешение записи для раздела A, заземлено. | Тактовый вход для секции A – это CL<sub>A</sub>. Данные поступают в CL<sub>A</sub>. Данные, задержанные на 64-тактовые импульсы, берутся из Q<sub>64A</sub>. WE<sub>A</sub>, разрешение записи для раздела A, заземлено. | ||

| Строка 189: | Строка 189: | ||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 195: | Строка 195: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника | {{Навигационная таблица/Портал/Электроника}} | ||

Текущая версия от 21:52, 22 мая 2023

Сдвиговые регистры: последовательный вход, последовательный выход (SISO)[1]

Сдвиговые регистры с последовательным вводом и выводом задерживают данные на один такт для каждого этапа.

Они хранят бит данных в каждом регистре. Сдвиговый регистр с последовательными входом и выходом обычно имеют длину от одного до 64 бит (но можно и больше), если регистры или пакеты каскадируются.

Ниже показан одноэтапный сдвиговый регистр, принимающий данные, которые не синхронизированы с тактовым входом регистра.

«Входные данных» на терминале типа «D» (D-триггере) не меняет уровни, когда тактовый сигнал меняется с «низкого» на «высокий».

Мы можем захотеть синхронизировать данные с общесистемными часами на печатной плате, чтобы повысить надёжность цифровой логической схемы.

Очевидный момент (по сравнению с рисунком 2 ниже), показанный на рисунке 1 выше, заключается в том, что любые «входные данные», присутствующие на терминале типа «D», передаются с D на выход Q за тактовое время.

Поскольку в нашем примере сдвиговый регистр использует элементы памяти, чувствительные к положительному фронту, выход Q следует за входом D, когда тактовый сигнал переходит от «низкого» уровня к «высокому», как показано стрелками вверх на рисунке 1 выше.

Несомненно, такой логический уровень присутствует во время тактового сигнала, потому что данные стабильны задолго до и после фронта тактового сигнала.

Это редко можно увидеть в многоэтапных сдвиговых регистрах. Но это простой пример для начала. Нас интересует только положительный фронт тактового сигнала, от «низкого» к «высокому».

Отрицательным фронтом можно пренебречь. Очень легко увидеть, что Q следует за D по тактам выше.

Сравните это с рисунком 2 ниже, где «входные данные» меняются с положительным фронтом тактового сигнала.

Поскольку «входные данные» изменяются за время t1 выше, что «видит» D-триггер за время такта?

Если кратенько, то он воспринимает данные, которые присутствовали в точке D до тактового сигнала.

Это то, что передаётся в Q в момент времени t1. Правильная волна на рисунке 2 – это QC. В момент t1 Q обращается в нуль, если он уже не равен нулю.

Регистр D не «видит» единицу до момента t2, когда Q становится «высоким».

Поскольку данные, указанные выше, присутствующие в D, синхронизируются с Q за тактовое время, а Q не может измениться до следующего такта, D-триггер задерживает данные на один тактовый период при условии, что данные уже синхронизированы с таковым входом. Волна QA такая же, как и для «входных данных» с задержкой в один тактовый период.

Далее следует более подробный взгляд на то, что «видит» вход триггера типа D за тактовое время.

См. рисунок 4 ниже. Поскольку «входные данные» меняются во времени (как на рисунке 3 выше), нам нужна дополнительная информация, чтобы определить, что именно «видит» D-триггер.

Если «входные данные» поступают из другого этапа сдвигового регистра, другого типа D-триггера, мы можем сделать некоторые выводы на основе информации из таблицы данных.

Производители цифровой логики предоставляют информацию о своих деталях в виде таблиц, которые ранее были доступны только в сборнике, называемом справочником данных.

Такие книжные справочники всё ещё в ходу; хотя в наше время более лучшим источником является веб-сайт производителя.

Следующие данные были взяты из технического описания CD4006b для работы при напряжении 5 В постоянного тока и служат в качестве примера для иллюстрации синхронизации.

- tS = 100 нс

- tH = 60 нс

- tP =200-400 нс тип./макс.

tS — время установки, данные о времени должны быть представлены в соответствии с часовым поясом. В этом случае данные должны быть представлены в D за 100 нс до тактового сигнала.

Кроме того, данные должны храниться в течение времени удержания tH = 60 нс после тактового импульса. Эти два условия должны быть выполнены для надёжной синхронизации данных от D до Q триггера.

С соблюдением времени установки 60 нс проблем не возникает, так как данные в D были там в течение всего предыдущего тактового периода, раз уж они поступают из другого этапа сдвигового регистра.

Например, при тактовой частоте 1 МГц тактовый период составляет 1000 мкс, это достаточно много времени.

Фактически данные будут присутствовать за 1000 мкс до тактового сигнала, что намного больше минимального требуемого tS в 60 нс.

Время удержания tH = 60 нс соблюдается, поскольку D, подключённый к Q другого каскада, не может изменяться быстрее, чем задержка распространения предыдущего каскада tP = 200 нс.

Время удержания сохраняется до тех пор, пока задержка распространения предыдущего D-триггера больше, чем это самое время удержания.

Данные в D, управляемые другим каскадом Q, не будут изменяться быстрее, чем за 200 нс для CD4006b.

Подводя итог, можно сказать, что выход Q следует за входом D примерно по тактовой частоте, если триггеры каскадированы в многоэтапный сдвиговый регистр.

Три триггера типа «D» соединены каскадом от Q к D, а тактовые импульсы соединены параллельно, образуя трёхкаскадный сдвиговый регистр.

JK-регистры формируют каскады Q в J, Q' в K с параллельными тактовыми импульсами, в результате чего получается альтернативная форма сдвигового регистра, описанная выше.

Сдвиговый регистр с последовательными входом и выходом имеет тактовый вход, ввод данных и вывод данных из последнего этапа.

Как правило, другие выходы каскада недоступны. В противном случае это был бы сдвиговый регистр с последовательным входом и параллельным выходом.

Приведённые на рисунке 7 ниже волны сигналов относятся к любой из двух предыдущих версий сдвигового регистра с последовательными входом и выходом.

Три пары стрелок показывают, что трёхступенчатый сдвиговый регистр временно хранит 3 бита данных и задерживает их на три такта от ввода до вывода.

В тактовое время t1 нули на «входных данных» синхронизируются от D до Q всех трёх этапов. В частности, D этапа A «видит» логический 0, который синхронизируется с QA, где он остаётся до момента времени t2.

В тактовое время t2 единицы на «входных данных» синхронизируется от D до QA. На стадиях B и C нули, поступающие с предыдущих стадий, синхронизируется с QB и QC.

В тактовое время t3 нули на «входных данных» синхронизируются от D до QA. QA становится «низким» и остаётся таковым для оставшихся тактов из-за того, что «входные данные» равны 0. QB становится «высоким» в момент t3 из-за 1 на предыдущем этапе. QC всё ещё остаётся «низким» после t3 из-за «низкого» уровня на предыдущем этапе.

QC, наконец, становится «высоким» на такте t4 из-за «высокого» уровня, подаваемого на D с предыдущего этапа QB. Всё более ранние этапы имеют смещенные в них 0. И после следующего тактового импульса в момент t5 все логические единицы будут смещены и заменены на нули.

Устройства с последовательным вводом/выводом

Мы более подробно рассмотрим следующие компоненты, доступные в виде интегральных схем, любезно предоставленные компанией Texas Instruments.

Для получения полных спецификаций на сайте компании нужно открыть страницы таких устройств.

- CD4006b 18-битный сдвиговый регистр с последовательным входом/выходом.

- CD4031b 64-битный сдвиговый регистр с последовательным входом/выходом.

- CD4517b двойной 64-битный сдвиговый регистр с последовательным входом/выходом.

Следующие регистры сдвига с последовательным входом/выходом относятся к семейству КМОП (комплементарных металлооксидных полупроводников) серии 4000.

Таким образом, они будут принимать VDD, положительный источник питания от 3 до 15 вольт. Вывод VSS заземлён.

Максимальная частота тактов сдвига, которая зависит от VDD, составляет несколько мегагерц.

18-битный CD4006b состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита.

Таким образом, 5-битные ступени можно использовать как 4-битные сдвиговые регистры.

Чтобы получить полный 18-битный сдвиговый регистр, выход одного сдвигового регистра должен быть каскадирован на вход другого и так далее, пока все каскады не создадут один сдвиговый регистр, как показано на рисунке 9 ниже.

18-битный CD4006b состоит из двух каскадов по 4 бита и ещё двух каскадов по 5 бит с выходным отводом на 4 бита.

64-битный сдвиговый регистр последовательного ввода/вывода CD4031 показан ниже.

Ряд контактов не подключены (отмечено как «н/п», т.е. нет подключения). И Q, и Q' доступны с 64-го этапа, на самом деле это Q64 и Q'64.

Существует также Q64, «отстоящий» на пол-этапа, который задерживается на половину тактового цикла. Основной особенностью является селекторный переключатель данных, который находится на входе данных в сдвиговый регистр.

«Управление режимом» выбирает между двумя входами: «Данные 1» или «Данные 2». Если «управление режимом» имеет «высокий» уровень, данные будут выбраны из «Данные 2» для входа в сдвиговый регистр.

В случае, когда «управление режимом» имеет «низкий» логический уровень, выбирается «Данные 1». Примеры этого показаны на двух рисунках ниже.

«Данные 2» на рисунке 11 выше подключены к выходу Q64 сдвигового регистра. При «высоком» уровне «управления режимом» выход Q64 направляется обратно на вход данных D-переключателя.

Данные будут циркулировать от вывода к вводу. Они будут повторяться каждые 64 тактовых импульса, как показано на рисунке 11 выше.

Возникает вопрос: как этот шаблон данных вообще попал в сдвиговый регистр?

Выходной сигнал Q64 не рециркулируется, поскольку «нижний» вентиль селектора данных отключён.

Под отключением мы подразумеваем, что «низкий» логический уровень «управления режимом», дважды инвертированный в «низкий» уровень на нижнем вентиле И-НЕ, предотвращает передачу любого сигнала на нижний контакт (Данные 2) на выход вентиля.

Таким образом, он отключён.

Двойной 64-битный сдвиговый регистр CD4517b показан на рисунке 13 выше. Обратите внимание на отводы на 16-й, 32-й и 48-й этапах.

Сие значит, что сдвиговые регистры такой длины можно сконфигурировать из одного из 64-битных сдвиговых регистров.

Само собой, 64-битные сдвиговые регистры могут быть каскадированы для получения 80-битного, 96-битного, 112-битного или 128-битного сдвигового регистра.

Тактовые входы CLA и CLB должны быть параллельны при каскадном включении двух переключателей. WEB и WEA, заземлённых для нормального переключения передач.

Входные данные в сдвиговые регистры A и B – это DA и DB соответственно.

Предположим, что нам требуется 16-битный регистр сдвига.

Можно ли это настроить с помощью CD4517b? Как насчёт 64-сдвигового регистра из той же части?

На рисунке 14 выше мы показываем A для CD4517b, подключённый как 16-битный регистр сдвига для секции B.

Тактовый вход этапа B – это CLB. Здесь данные синхронизируются. А данные, задержанные на 16 тактов, снимаются Q16B. WEB, разрешающая запись, заземлено.

Выше мы также показываем тот же CD4517b, подключённый в качестве 64-битного сдвигового регистра для независимой секции A.

Тактовый вход для секции A – это CLA. Данные поступают в CLA. Данные, задержанные на 64-тактовые импульсы, берутся из Q64A. WEA, разрешение записи для раздела A, заземлено.

См.также

Внешние ссылки