Электроника:Цифровая электроника/Логические вентили/Транзисторно-транзисторная логика вентилей «ИЛИ-НЕ» и «ИЛИ»: различия между версиями

Valemak (обсуждение | вклад) |

Нет описания правки |

||

| (не показаны 4 промежуточные версии 2 участников) | |||

| Строка 15: | Строка 15: | ||

[[File:IV-3_6_2.png|400px|center|thumb|'''Рис. 2.''' Для анализа вентильной ТТЛ-схемы заменим Q<sub>1</sub> и Q<sub>2</sub> на пары управляющих диодов для наглядности.|alt=Рис. 2. Для анализа вентильной ТТЛ-схемы заменим Q1 и Q2 на пары управляющих диодов для наглядности.]] | [[File:IV-3_6_2.png|400px|center|thumb|'''Рис. 2.''' Для анализа вентильной ТТЛ-схемы заменим Q<sub>1</sub> и Q<sub>2</sub> на пары управляющих диодов для наглядности.|alt=Рис. 2. Для анализа вентильной ТТЛ-схемы заменим Q1 и Q2 на пары управляющих диодов для наглядности.]] | ||

Если вход A оставить «плавающим» (другими словами, подключённым к V<sub> | Если вход A оставить «плавающим» (другими словами, подключённым к V<sub>КК</sub>), ток будет проходить через базу [[транзистор]]а Q<sub>3</sub>, насыщая его. Если вход A заземлён, этот ток отводится от базы Q<sub>3</sub> через левый управляющий диод из «Q<sub>1</sub>», тем самым заставляя Q<sub>3</sub> отключаться. То же самое можно сказать о входе B и [[транзистор]]е Q<sub>4</sub>: логический уровень входа B определяет проводимость Q<sub>4</sub>: там либо насыщение, либо отсечка. | ||

Обратите внимание, как запараллелены | Обратите внимание, как запараллелены [[транзистор]]ы Q<sub>3</sub> и Q<sub>4</sub> через их выводы [[коллектор]]а и [[эмиттер]]а. По сути, эти два [[транзистор]]а действуют как параллельные переключатели, пропуская ток через [[резистор]]ы R<sub>3</sub> и R<sub>4</sub> в соответствии с логическими уровнями входов A и B. Если какой-либо вход находится на «высоком» (1) уровне, то хотя бы один из двух [[транзистор]]ов (Q<sub>3</sub> и/или Q<sub>4</sub>) будет насыщен (или будут насыщены оба), пропуская ток через [[резистор]]ы R<sub>3</sub> и R<sub>4</sub>, и включив конечный выходной [[транзистор]] Q<sub>5</sub> для вывода «низкого» (0) логического уровня. В единственном случае, когда выход этой схемы может перейти в «высокое» (1) состояние – это если оба [[транзистор]]а (одновременно и Q<sub>3</sub> и Q<sub>4</sub>) отключены, что означает, что оба входа должны быть заземлены, другими словами, иметь «низкий» (0) логический уровень. | ||

== Таблица истинности вентиля «ИЛИ-НЕ» == | == Таблица истинности вентиля «ИЛИ-НЕ» == | ||

Таким образом, таблица истинности для этой схемы эквивалентна таблице истинности логического элемента ИЛИ-НЕ: | Таким образом, таблица истинности для этой схемы эквивалентна таблице истинности логического элемента [[ИЛИ-НЕ]]: | ||

[[File:IV-3_6_3.png|400px|center|thumb|'''Рис. 3.''' Таблица истинности вентиля ИЛИ-НЕ.|alt=Рис. 3. Таблица истинности вентиля ИЛИ-НЕ.]] | [[File:IV-3_6_3.png|400px|center|thumb|'''Рис. 3.''' Таблица истинности вентиля [[ИЛИ-НЕ]].|alt=Рис. 3. Таблица истинности вентиля ИЛИ-НЕ.]] | ||

== Преобразование ТТЛ-схемы вентиля «ИЛИ-НЕ» в ТТЛ-схему вентиля «ИЛИ» == | |||

Чтобы превратить эту схему вентиля ИЛИ-НЕ в вентиль ИЛИ, нужно инвертировать выходной логический уровень с помощью другого транзисторного каскада, как мы это сделали в прошлом разделе с примером вентиля И-НЕ при преобразовании его в вентиль И: | Чтобы превратить эту схему вентиля [[ИЛИ-НЕ]] в вентиль [[ИЛИ]], нужно инвертировать выходной логический уровень с помощью другого транзисторного каскада, как мы это сделали в прошлом разделе с примером вентиля И-НЕ при преобразовании его в вентиль И: | ||

[[File:IV-3_6_4.png|400px|center|thumb|'''Рис. 4.''' Вентиль ИЛИ с выходом с открытым | [[File:IV-3_6_4.png|400px|center|thumb|'''Рис. 4.''' Вентиль ИЛИ с выходом с открытым [[коллектор]]ом.|alt=Рис. 4. Вентиль ИЛИ с выходом с открытым коллектором.]] | ||

== Таблица истинности вентиля «ИЛИ» == | == Таблица истинности вентиля «ИЛИ» == | ||

Тут показаны таблица истинности и эквивалентная схема вентиля ИЛИ (на которой изображён вентиль ИЛИ-НЕ с инвертированным выходом): | Тут показаны таблица истинности и эквивалентная схема вентиля ИЛИ (на которой изображён вентиль ИЛИ-НЕ с инвертированным выходом): | ||

| Строка 39: | Строка 40: | ||

== Итог == | == Итог == | ||

*Вентиль ИЛИ можно создать, добавив каскад с инвертором к выходу вентиля ИЛИ-НЕ. | |||

* Вентиль ИЛИ можно создать, добавив каскад с инвертором к выходу вентиля ИЛИ-НЕ. | |||

=См.также= | =См.также= | ||

=Внешние ссылки= | =Внешние ссылки= | ||

| Строка 49: | Строка 51: | ||

<references /> | <references /> | ||

{{Навигационная таблица/Электроника}} | {{Навигационная таблица/Портал/Электроника}} | ||

[[Категория:Цифровая электроника]] | [[Категория:Цифровая электроника]] | ||

[[Категория:Логические вентили]] | [[Категория:Логические вентили]] | ||

[[Категория:Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»]] | [[Категория:Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»]] | ||

[[Категория:Вентиль «И»]] | [[Категория:Вентиль «И»]] | ||

[[Категория:Вентиль «И-НЕ»]] | [[Категория:Вентиль «И-НЕ»]] | ||

Текущая версия от 21:52, 22 мая 2023

Транзисторно-транзисторная логика вентилей «ИЛИ-НЕ» и «ИЛИ»[1]

Анализ ТТЛ вентилей

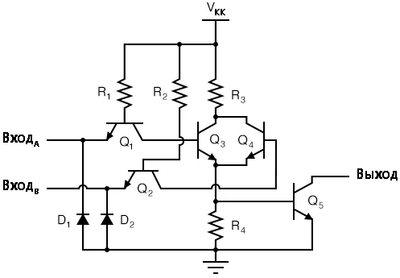

Рассмотрим такую ТТЛ-схему и проанализируем её работу:

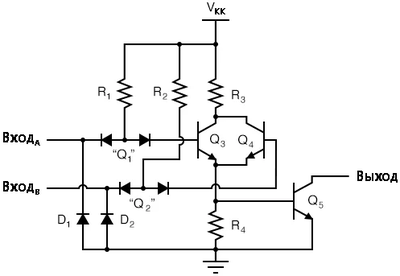

Транзисторы Q1 и Q2 расположены таким же образом, как и транзистор Q1 в других ТТЛ-схемах из предыдущих лекций. Вместо того, чтобы работать как усилители, и Q1 и Q2 используются как двухдиодные «управляющие» контуры. Заменим Q1 и Q2 на наборы диодов, чтобы это проиллюстрировать:

Если вход A оставить «плавающим» (другими словами, подключённым к VКК), ток будет проходить через базу транзистора Q3, насыщая его. Если вход A заземлён, этот ток отводится от базы Q3 через левый управляющий диод из «Q1», тем самым заставляя Q3 отключаться. То же самое можно сказать о входе B и транзисторе Q4: логический уровень входа B определяет проводимость Q4: там либо насыщение, либо отсечка.

Обратите внимание, как запараллелены транзисторы Q3 и Q4 через их выводы коллектора и эмиттера. По сути, эти два транзистора действуют как параллельные переключатели, пропуская ток через резисторы R3 и R4 в соответствии с логическими уровнями входов A и B. Если какой-либо вход находится на «высоком» (1) уровне, то хотя бы один из двух транзисторов (Q3 и/или Q4) будет насыщен (или будут насыщены оба), пропуская ток через резисторы R3 и R4, и включив конечный выходной транзистор Q5 для вывода «низкого» (0) логического уровня. В единственном случае, когда выход этой схемы может перейти в «высокое» (1) состояние – это если оба транзистора (одновременно и Q3 и Q4) отключены, что означает, что оба входа должны быть заземлены, другими словами, иметь «низкий» (0) логический уровень.

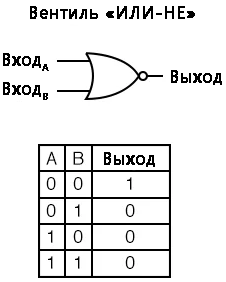

Таблица истинности вентиля «ИЛИ-НЕ»

Таким образом, таблица истинности для этой схемы эквивалентна таблице истинности логического элемента ИЛИ-НЕ:

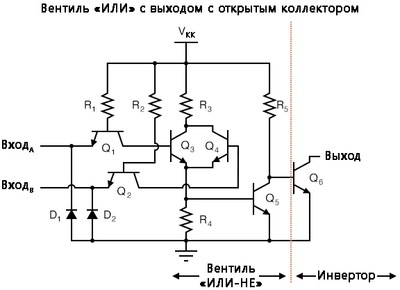

Преобразование ТТЛ-схемы вентиля «ИЛИ-НЕ» в ТТЛ-схему вентиля «ИЛИ»

Чтобы превратить эту схему вентиля ИЛИ-НЕ в вентиль ИЛИ, нужно инвертировать выходной логический уровень с помощью другого транзисторного каскада, как мы это сделали в прошлом разделе с примером вентиля И-НЕ при преобразовании его в вентиль И:

Таблица истинности вентиля «ИЛИ»

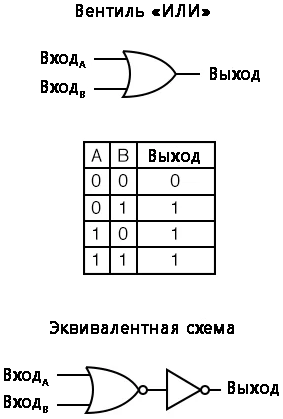

Тут показаны таблица истинности и эквивалентная схема вентиля ИЛИ (на которой изображён вентиль ИЛИ-НЕ с инвертированным выходом):

Разумеется, в этих логических ТТЛ-схемах для ИЛИ-НЕ и ИЛИ можно использовать каскады с выходом «тотемный столб» (как это было для вентилей И-НЕ и И из прошлой лекции).

Итог

- Вентиль ИЛИ можно создать, добавив каскад с инвертором к выходу вентиля ИЛИ-НЕ.

См.также

Внешние ссылки

- Электроника

- Перевод:valemak

- Перевод от valemak

- Перевёл valemak

- Проверка:myagkij

- Оформление:myagkij

- Редактирование:myagkij

- Страницы, где используется шаблон "Навигационная таблица/Телепорт"

- Страницы с телепортом

- Цифровая электроника

- Логические вентили

- Транзисторно-транзисторная логика вентилей «И-НЕ» и «И»

- Вентиль «И»

- Вентиль «И-НЕ»